1.DSP芯片發(fā)展

隨著DSP芯片應(yīng)用領(lǐng)域的不斷擴大,DSP芯片已形成低、中、高三個檔次:低端產(chǎn)品執(zhí)行速度一般為20~50MIPS,能維持適量存儲和功耗,提供了較好的性能價格比,適用于儀器儀表和精密控制等;中端產(chǎn)品執(zhí)行速度一般為100 ~150MIPS,結(jié)構(gòu)較為復(fù)雜,具有較高的處理速度和低的功耗,適用于無線電信設(shè)備和高速解調(diào)器等;高端產(chǎn)品執(zhí)行速度一般為1O00MIPS 以上,處理速度很高,產(chǎn)品結(jié)構(gòu)多樣化,適用于圖像技術(shù)和智能通信基站等。

對于種類繁多的DSP芯片,一般可按其工作的數(shù)據(jù)格式將其分為兩大類定點DSP芯片和浮點DSP芯片。定點DSP品種最多,處理速度為20 ~240OMIPS;浮點DSP處理速度為40M ~ 1GFLOPS。

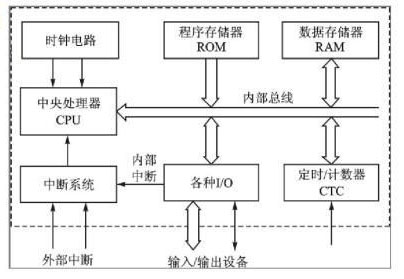

圖1 DSP芯片

2.DSP芯片結(jié)構(gòu)

DSP芯片是專為高速信號處理而設(shè)計的,由于采用了不同于普通單片機的體系結(jié)構(gòu),因而具有一些顯著的特點。

2.1哈佛結(jié)構(gòu)

傳統(tǒng)的馮諾伊曼( Von-Neumann)結(jié)構(gòu)由于具有單一公用的數(shù)據(jù)和指令總線,因此在高速運算時,往往在傳輸通道上會出現(xiàn)瓶頸效應(yīng)。DSP芯片內(nèi)部一般采用哈佛(Harvard)結(jié)構(gòu),片內(nèi)至少有四套總線:程序的數(shù)據(jù)總線與地址總線,數(shù)據(jù)的數(shù)據(jù)總線與地址總線。這種分離的程序總線和數(shù)據(jù)總線,可允許在一個機器周期內(nèi)同時獲取指令字(來自程序存儲器)和操作數(shù)(來自數(shù)據(jù)存儲器),從而提高了執(zhí)行速度。

2.2硬件乘法器

數(shù)字信號處理中最重要的一個基本運算是乘法累加運算,也是最主要和最耗時的運算,因此單周期的硬件乘法器是 DSP芯片實現(xiàn)快速運算的保證。現(xiàn)代高性能的DSP芯片甚至具有兩個以上的硬件乘法器用以提高運算速度。數(shù)據(jù)寬度也從16位增加到32位。

2.3多個并行處理單元

DSP內(nèi)部一般都集成了多個處理單元,如硬件乘法器(MUL)、累加器(ACC)、算術(shù)邏輯單元(ALU)、輔助算術(shù)單元(ARAU)以及 DMA控制器等。它們都可以并行地在同一個周期內(nèi)執(zhí)行不同的任務(wù),例如輔助算術(shù)單元能為下一次的運算做好準(zhǔn)備,適合于完成連續(xù)的乘加運算。芯片內(nèi)部還包括有其他總線,如 DMA總線等,可實現(xiàn)數(shù)據(jù)的后臺傳輸而幾乎不影響主 CPU的性能的有FFT的位反轉(zhuǎn)尋址,語音的A律、p律算法等。

為了提高并行處理能力,現(xiàn)代DSP芯片通常采用單指令多數(shù)據(jù)流結(jié)構(gòu)(SIMD)、超長指令字結(jié)構(gòu)(VLIW)、超標(biāo)量體系結(jié)構(gòu)、多DSP核體系結(jié)構(gòu)和DSP/MCU混合結(jié)構(gòu),這些并行處理機制大大提高了DSP芯片的性能。

2.4流水線技術(shù)

DSP芯片的哈佛結(jié)構(gòu)為流水線技術(shù)提供了方便。由于采用流水線技術(shù),DSP芯片可以單周期完成乘沃累加運算,大大提高了運算速度。而DSP芯片的指令基本上都是單周期指令,因此單周期指令執(zhí)行時間可以作為衡量DSP芯片性能的一個主要指標(biāo)。

2.5片上存儲器

外部存儲器一般不能適應(yīng)高性能DSP核的處理速度,因此在片上設(shè)置較大的程序/數(shù)據(jù)存儲器以減少對外部存儲器中程序/數(shù)據(jù)的訪問次數(shù),充分發(fā)揮DSP核的高性能。目前高性能DSP芯片上的可配置程度/數(shù)據(jù)RAM高達7MB。采用大的片子存儲器可以減少外部存儲器接口的引腳,甚至省略外部存儲器接口,而且也減小了芯片的封裝體積。

2.6多種外設(shè)和接口

為了加強 DSP芯片的通用性,DSP芯片上增加了許多外設(shè)??赡馨ǖ耐庠O(shè)有:多路DMA通道、外部主機接口、外部存儲器接口、芯片間高速鏈接口、外部中斷、通信串口、定時器、可編程鎖相環(huán)、A/D轉(zhuǎn)換器、JTAG接口等。

2.7特殊尋址模式

為了滿足FFT積等數(shù)字信號處理的特殊要求,DSP芯片大多包含專門的硬件地址產(chǎn)生器,用以實現(xiàn)循環(huán)尋址和位翻轉(zhuǎn)尋址,并在軟件上設(shè)置了相應(yīng)的指令。

2.8零消耗循環(huán)控制

數(shù)字信號處理的一大特點是大部分處理時間花在了較小循環(huán)的少量核心代碼上。大部分DSP芯片具有零消耗循環(huán)控制的專門硬件,可以省去循環(huán)計數(shù)器的測試指令,從而提高了代碼效率,減少了執(zhí)行時間。

2.9JTAG接口

由于DSP芯片結(jié)構(gòu)的復(fù)雜化、工作速度的提高、外部引腳的增多、封裝面積減小而導(dǎo)致的引腳排列密集等原因,傳統(tǒng)的并行仿真方式已不適合于DSP芯片的發(fā)展和應(yīng)用開發(fā)。1991年公布的JTAG接口標(biāo)準(zhǔn)滿足了IC制造商和用戶的要求,1993年 JTAG接口標(biāo)準(zhǔn)修訂為5線接口。在片JTAG接口為 DSP芯片的測試和仿真提供了很大的便利。

2.10程序的加載引導(dǎo)

加載引導(dǎo)是指器件在上電復(fù)位后執(zhí)行一段引導(dǎo)程序,用于從端口(異步串口、I/O口、主機接口)或外部EPROM/FLASH存儲器中加載程序至高速RAM中運行。一般用 EPROM/FLASH存儲器存儲程序,但是其訪問速度較慢,而一些已有的高速EPROM/FLASH存儲器價格昂貴且容量有限;同時高速大容量靜態(tài)RAM價格又在不斷下降,因此這種加載方式是一個有效的性價比解決方法。

3.在圖像技術(shù)中的應(yīng)用

目前實現(xiàn)圖像處理的主要方式有四種:①基于通用PC微機;②基于通用DSP芯片;③基于專用DSP芯片;④基于可編程FPGA。在通用PC微機上主要是軟件實現(xiàn)圖像處理,能夠提供中等的圖像處理能力,但是要占用CPU幾乎全部的處理能力。在獨立機型設(shè)計中一般采用其他三種方式:①基于可編程FPGA的設(shè)計比較復(fù)雜而且難度較大;②基于專用DSP芯片的設(shè)計應(yīng)用范圍受限;③基于通用DSP芯片設(shè)計的優(yōu)點是設(shè)計簡便、靈活,特別適合于新型產(chǎn)品的研究開發(fā)。

3.1圖像技術(shù)對DSP芯片的要求

對于圖像技術(shù)來說,由于要處理的數(shù)據(jù)量大,計算復(fù)雜,計算中間結(jié)果精度要求高,因此需要選擇合適的DSP芯片。在選擇DSP芯片時首先要考慮對芯片速度的要求。由于現(xiàn)代高性能DSP芯片的結(jié)構(gòu)多樣化,單純依靠指令執(zhí)行速度MIPS 比較其性能是不全面的,現(xiàn)在一般采用單周期的乘加次數(shù),或采用數(shù)字信號處理中的基準(zhǔn)程序如FFT和數(shù)字濾波等的執(zhí)行時間來測評DSP芯片的速度性能。其次,還需要考慮如何選擇定點或浮點DSP芯片。

一般說來,浮點DSP芯片的運算精度高,動態(tài)范圍大,尋址空間大,指令運算能力較強,但功耗、成本、體積較大。而定點DSP芯片的運算精度與浮點DSP芯片相同(定點的數(shù)據(jù)位數(shù)和浮點的位數(shù)相同的情況下),且功耗、成本、體積較小,但動態(tài)范圍小,需要防止計算溢出,尋址空間小,指令運算能力較弱。從總體性能上看,浮點DSP芯片優(yōu)于定點DSP芯片。此外,在硬件方面還應(yīng)考慮芯片的外部總線結(jié)構(gòu)、片上存儲器結(jié)構(gòu)、DMA功能、串行通信口和芯片間通信能力等因素;在軟件方面主要是開發(fā)軟件的功能性、開發(fā)時間要求等因素。

綜合考慮DSP芯片的性能和開發(fā)設(shè)計的要求后,在圖像技術(shù)中應(yīng)該首選浮點DSP芯片,但是在對價格敏感的產(chǎn)品設(shè)計中,目前采用定點DSP芯片的例子也有。

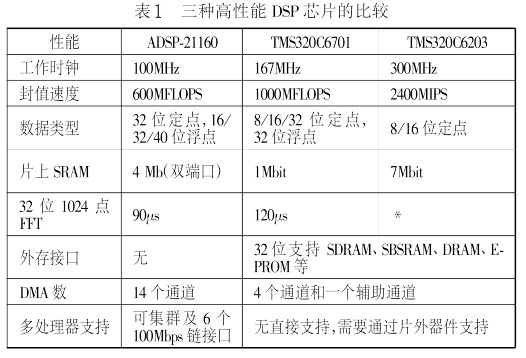

表1比較了代表目前很高DSP芯片技術(shù)水平的三種產(chǎn)品,包括TI公司的定點 DSP芯片(TMS320C6203)和浮點DSP芯片(TMS320C6701)與AD公司浮點DSP芯片(ADSP-21160)。由于工作時鐘較高的原因,TI公司的DSP芯片在單芯片處理能力上優(yōu)于AD公司的產(chǎn)品,但是在多芯片集成處理上AD公司的DSP芯片性能更好一些。

3.2基于DSP芯片的圖像處理系統(tǒng)

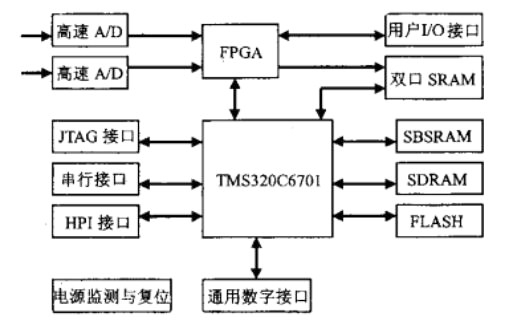

圖2所示為一個獨立型通用圖像處理系統(tǒng)。系統(tǒng)板主要構(gòu)成為:工作于167MHz的TMS320C6701 ; 32位4M的SDRAM ,32位128K 的SBSRAM,32位4K的雙口RAM,16位1M的Flash存儲器;兩路A/D,每路40M/12Bit,可同時采樣,采樣頻率可變;可編程FPGA作為靈活的接口;通用數(shù)字接口也可以直接接收彩色數(shù)字圖像;外部HPI主機接口可用于系統(tǒng)控制;仿真調(diào)試JTAG接口;串行通信接口;電源監(jiān)測與復(fù)位控制電路等。

在該系統(tǒng)開發(fā)板上處理應(yīng)用于會議電視的CIF格式的彩色圖像,實驗效果較好。TI公司提供了全圖形的Code Composer集成開發(fā)環(huán)境,具有匯編語言和直接的C編譯器。匯編語言的程序代碼執(zhí)行效率高,而采用C語言的程序代碼效率較差。但是,直接采用匯編語言編程有一定難度。因此,通常先采用c語言設(shè)計驗證算法,然后經(jīng)過C編譯器產(chǎn)生匯編代碼。最后在匯編代碼的基礎(chǔ)上進行優(yōu)化。

圖2 獨立型通用圖像處理系統(tǒng)框圖

結(jié)束語

以上就是DSP芯片在圖像技術(shù)中的應(yīng)用介紹了。DSP芯片將應(yīng)用在更多的領(lǐng)域,如智能通信基站、雷達、聲納、圖形圖像系統(tǒng)、語音識別、VOIP、飛行仿真、軍用設(shè)備等等。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報價以及產(chǎn)品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280