隨著數(shù)字技術(shù)的飛速發(fā)展,高精度大動(dòng)態(tài)范圍數(shù)字/模擬(D/A)轉(zhuǎn)換器的出現(xiàn)和廣泛應(yīng)用,用數(shù)字控制方法從一個(gè)標(biāo)準(zhǔn)參考頻率源產(chǎn)生多個(gè)頻率信號(hào)的技術(shù),即直接數(shù)字合成(DDS)技術(shù)異軍突起;其具有分辨率高、頻率變換快、相位噪聲低,信號(hào)純度高等優(yōu)點(diǎn),因此,在雷達(dá)及通信等領(lǐng)域有著廣泛的應(yīng)用前景。文中介紹了一種高性能DDS芯片AD9850的基本原理和工作特點(diǎn),闡述了如何利用此芯片設(shè)計(jì)一種頻率在0~50kHz內(nèi)變化、相位正交的信號(hào)源,給出了AD9850芯片和MCS51單片機(jī)的硬件接口和軟件流程。

1.AD9850芯片介紹

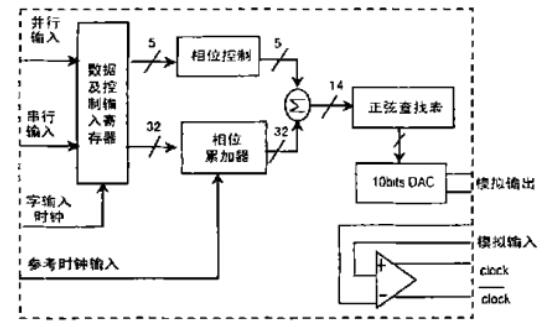

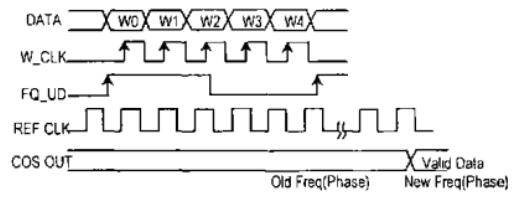

AD9850是AD 公司生產(chǎn)的最高時(shí)鐘為125MHz、采用先進(jìn)的CMOS技術(shù)的直接頻率合成器,主要由可編程DDS系統(tǒng)、高性能模數(shù)變換器(DAC)和高速比較器3部分構(gòu)成,能實(shí)現(xiàn)全數(shù)字編程控制的頻率合成,并具有時(shí)鐘產(chǎn)生功能,其原理框圖如圖1所示。

圖1 AD9850原理框圖

AD9850的DDS系統(tǒng)包括相位累加器和正弦查找表,其中相位累加器由一個(gè)加法器和一個(gè)32位相位寄存器組成,相位寄存器的輸出與外部相位控制字(5位)相加后作為正弦查找表的地址。正弦查找表實(shí)際上是一個(gè)相位/幅度轉(zhuǎn)換表,它包含一個(gè)正弦波周期的數(shù)字幅度信息,每一個(gè)地址對(duì)應(yīng)正弦波中0~3608范圍的一個(gè)相位點(diǎn)。查找表把輸入地址的相位信息映射成正弦波幅度信號(hào),然后驅(qū)動(dòng)10 bit的DA變換器,輸出2個(gè)互補(bǔ)的電流,其幅度可通過外接電阻進(jìn)行調(diào)節(jié)。AD9850還包括一個(gè)高速比較器,將DA變換器的輸出經(jīng)外部低通濾波器后接到此比較器上即可產(chǎn)生一個(gè)抖動(dòng)很小的方波,這使得AD9850可以方便地用作時(shí)鐘發(fā)生器。

AD9850包含40位頻率/相位控制字,可通過并行或串行方式送入器件:并行方式指連續(xù)輸入5次,每次同時(shí)輸入8位(1個(gè)字節(jié));串行方式則是在一個(gè)管腳完成40位串行數(shù)據(jù)流的輸入。這40位控制字中有32位用于頻率控制,5位用于相位控制,1位用于掉電( power down)控制,2位用于選擇工作方式。

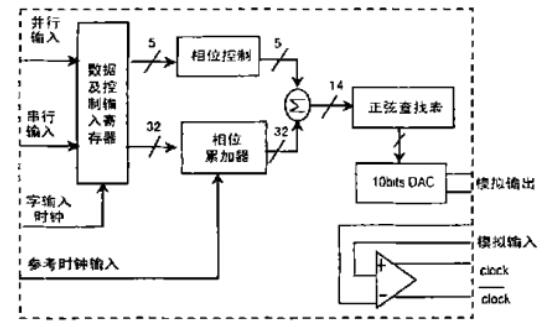

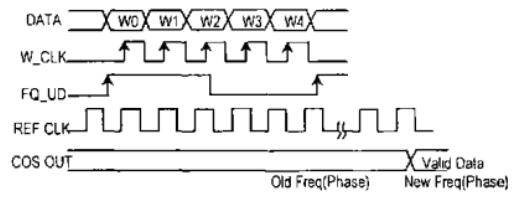

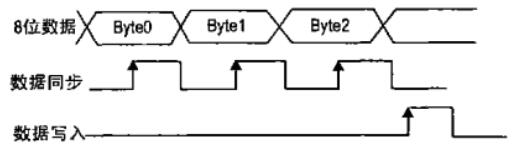

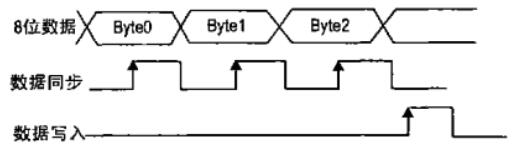

在并行輸入方式下,通過8位總線DO~D7將外部控制字輸入到寄存器,在 W_ CLK(字輸入時(shí)鐘)的上升沿裝入第一個(gè)字節(jié),并把指針指向下一個(gè)輸入寄存器,連續(xù)5個(gè)W- CLK 的上升沿讀入5個(gè)字節(jié)數(shù)據(jù)到輸入寄存器后,W- CLK的邊沿就不再起作用。然后在FQ-UD(頻率更新時(shí)鐘)上升沿到來時(shí)將這40位數(shù)據(jù)從輸入寄存器裝入到頻率/相位寄存器,這時(shí)DDS輸出頻率和相位更新一次,同時(shí)把地址指針復(fù)位到第一個(gè)輸入寄存器以等待下一次的頻率/相位控制字輸入。圖2即為AD9850控制字并行輸入時(shí)序。

圖2 控制字并行輸入時(shí)序

2.硬件設(shè)計(jì)

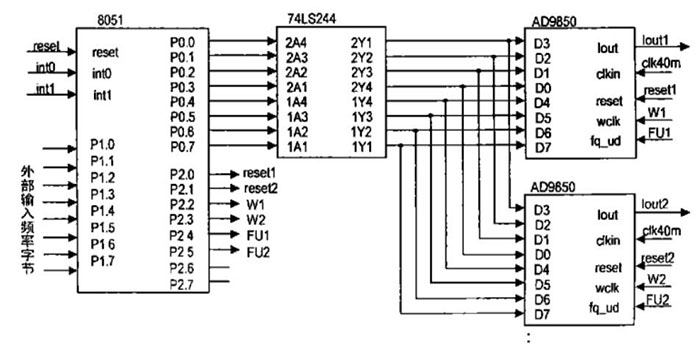

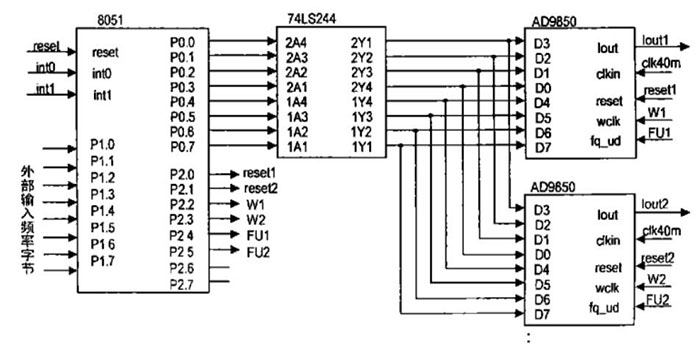

要產(chǎn)生兩路相位正交、頻率可由外部控制的正弦信號(hào),必須通過單片機(jī)編程來完成外部輸入的頻率數(shù)據(jù)(3個(gè)字節(jié))與DDS芯片(AD9850)內(nèi)部頻率相位控制字(5個(gè)字節(jié))間的轉(zhuǎn)換。單片機(jī) 8051與AD9850芯片的接口既可采用并行方式,也可采用串行方式,本設(shè)計(jì)采用的是8位并行接口方式。

由于需要產(chǎn)生I/Q兩路正弦信號(hào),因此使用了2片AD9850芯片,這兩路的頻率相同,相位差90°。單片機(jī)8051的P1口( P1.0~P1.7腳)用作外部空市字輸入,通過中斷1和中斷0讀入外部頻率數(shù)據(jù),連續(xù)讀3次,對(duì)應(yīng)頻率值的二進(jìn)制數(shù);單片機(jī)的P0口( P0.0~ P0.7腳)用作頻率/相位控制字輸出,通過8位緩沖器74LS244作數(shù)據(jù)緩沖后加到2片AD9850芯片的8位控制字輸入端(D0~D7腳),同時(shí)產(chǎn)生相應(yīng)的DDS時(shí)序控制信號(hào)(一路復(fù)位reset l、二路復(fù)位reset2、一路字輸入時(shí)鐘W1、二路字輸入時(shí)鐘W2、一路頻率更新時(shí)鐘FU 1、二路頻率更新時(shí)鐘FU2) 加到AD9850芯片的對(duì)應(yīng)管腳。AD9850的外部參考時(shí)鐘信號(hào)( clk40m)頻率為40 MHz,由晶體振蕩器產(chǎn)生。單片機(jī)8051的復(fù)位信號(hào)(reset )、中斷0和中斷1控制信號(hào)( int0、int 1)由外部控制系統(tǒng)給出,從而實(shí)現(xiàn)例路相位正交、頻率可控的正弦信號(hào)。該DDS信號(hào)源的硬件接口電路如圖3所示。

圖3 DDS信號(hào)源硬件接口電路圖

3.軟件控制

此程序的功能就是要將外部輸入的頻率數(shù)據(jù)按照一定協(xié)議和算法變換成DDS芯片(AD9850)所能接受的格式,并送出相應(yīng)的頻率相位控制信號(hào),從而使AD9850能產(chǎn)生兩路相位正交、頻率可控的正弦信號(hào)。下面給出程序設(shè)計(jì)輸入、輸出、變換算法及流程圖。

3.1輸入

數(shù)據(jù)同步:上升沿時(shí)讀入1個(gè)字節(jié)的頻率數(shù)據(jù),作為int1中斷輸入:

數(shù)據(jù)寫入:上升沿時(shí)頻率更新1次,作為int0中斷輸入;

8位數(shù)據(jù):輸入的頻率字節(jié)。分3次輸入,如圖4所示。

圖4 信號(hào)源控制程序輸入

3.2輸出

單片機(jī)控制程序?qū)a(chǎn)生下述輸出信號(hào)加到DDS芯片(AD9850)的對(duì)應(yīng)腳:

resetl:一路DDS復(fù)位(一路AD9850第22腳);

reset2:二路DDS復(fù)位(二路AD9850第22腳);

w 1:一路數(shù)據(jù)同步(一路AD9850第7腳);

w2:二路數(shù)據(jù)同步(二路AD9850第7腳);

ful:一路數(shù)據(jù)寫入(一路 AD9850第8腳);

fu2:二路數(shù)據(jù)寫入(二路AD9850第8腳);

PO 口(P0.0~P0.7):8位頻率/相位數(shù)據(jù)輸出( AD9850的D0~ D7腳)。

3.3算法

程序中單片機(jī)輸入頻率數(shù)據(jù)F(3個(gè)字節(jié))與輸出頻率數(shù)據(jù)?P( 4個(gè)字節(jié))間的變換算法見下式:

其中CIKN為外部參考時(shí)鐘( 40 000 000 Hz)。

3.4程序流程

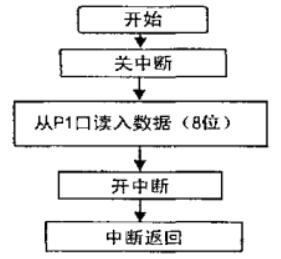

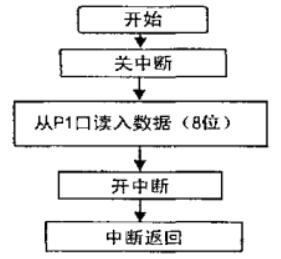

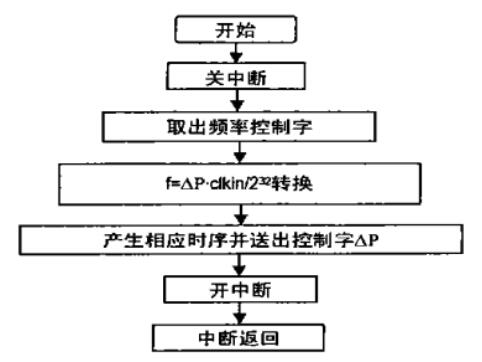

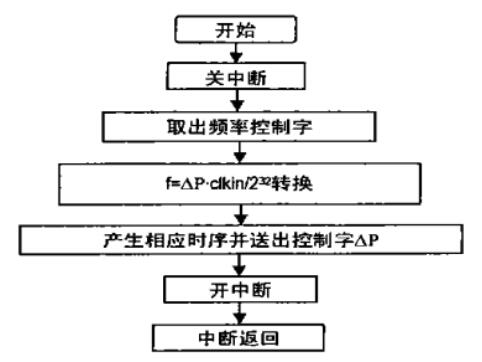

整個(gè)程序由主程序、中斷0子程序、中斷1子程序三部分構(gòu)成。主程序流程如圖5所示,中斷1子程序流程如圖6所示,中斷0子程序流程如圖7所示。

圖5 主程序流程圖

圖6 中斷1子程序流程圖

圖7 中斷0子程序流程圖

小結(jié)

以上就是基于DDS芯片AD9850的信號(hào)源設(shè)計(jì)介紹了。通過對(duì)設(shè)計(jì)的DDS信號(hào)源在不同頻率下的輸出波形進(jìn)行了測試,結(jié)果完全能達(dá)到所要求的性能指標(biāo)。目前廣泛應(yīng)用于電子測量、跳頻通信、雷達(dá)系統(tǒng)等領(lǐng)域。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

聯(lián)系號(hào)碼:18923864027(同微信)

QQ:709211280