艾目前,隨著一些便攜式電子系統(tǒng),如筆記本電腦、PDA、手機(jī)等的廣泛應(yīng)用,集成電路的功耗也被提到與面積和速度同等重要的位置。如果仍使用傳統(tǒng)的技術(shù),就可能負(fù)擔(dān)相當(dāng)重量的電池,或者電池的使用時(shí)間相當(dāng)短;而隨著集成電路集成度的提高,在設(shè)計(jì)時(shí)若不考慮功耗問(wèn)題,可能會(huì)使電路某些部分因功耗過(guò)大引起溫度過(guò)高,導(dǎo)致系統(tǒng)工作不穩(wěn)定或失效;功耗過(guò)大也會(huì)給封裝帶來(lái)很大困難,因此本文分別對(duì)CMOS集成電路的功耗來(lái)源和低功耗的設(shè)計(jì)方法及設(shè)計(jì)工具等進(jìn)行了介紹。

1.CMOS電路功耗的來(lái)源

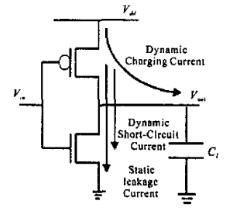

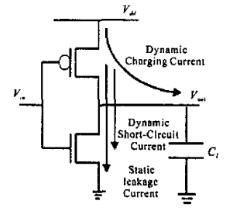

CMOS電路中有兩種主要的功耗來(lái)源:靜態(tài)功耗和動(dòng)態(tài)功耗。其中,動(dòng)態(tài)功耗包括短路電流引起的功耗(稱(chēng)為直流開(kāi)關(guān)功耗或短路功耗,發(fā)生在躍變過(guò)程中雙管同時(shí)導(dǎo)通引起的瞬態(tài)電流而形成的功耗)和負(fù)載電容的功耗(稱(chēng)為交流開(kāi)關(guān)功耗,由對(duì)負(fù)載電容充放電電流引起的功耗);靜態(tài)功耗主要是由漏電流引起的功耗(圖1)。

圖1CMOS集成電路功耗

1.1動(dòng)態(tài)功耗

(1)交流開(kāi)關(guān)功耗

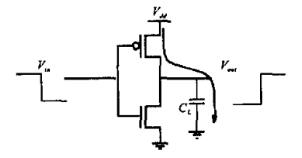

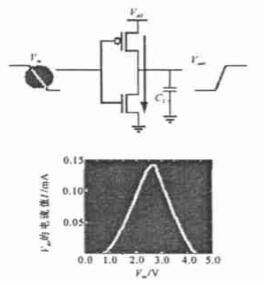

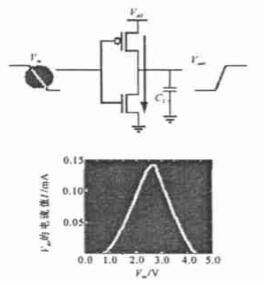

當(dāng)反相器的輸入為理想階躍波時(shí),對(duì)純電容負(fù)載CL充放電所消耗的功率為交流開(kāi)關(guān)功耗(圖2)。CMOS反相器的平均動(dòng)態(tài)功耗為:

式中,a為開(kāi)關(guān)系數(shù),即每個(gè)時(shí)鐘周期中發(fā)生狀態(tài)變化器件的個(gè)數(shù),CL為負(fù)載電容,f為電路的工作頻率,Vdd為電路的電源電壓值。

圖2CMOS電路的交流開(kāi)關(guān)功耗

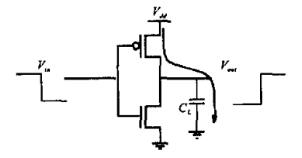

(2)直流開(kāi)關(guān)功耗

當(dāng)反相器輸入為非理想階躍波時(shí),在輸入波上升沿或下降沿瞬間,存在Р管和N管同時(shí)導(dǎo)通的區(qū)域,由此引起的功耗稱(chēng)直流開(kāi)關(guān)功耗或短路功耗。其值為:

式中,Vdd為電路的電源電壓值,Isr為短路電流值(見(jiàn)圖3)

圖3CMOS電路的直流開(kāi)關(guān)功耗

1.2靜態(tài)功耗

從理論上講,CMOS電路在穩(wěn)定狀態(tài)下沒(méi)有從電源到地的直接路徑,所以沒(méi)有靜態(tài)功耗。然而,在實(shí)際情況下,擴(kuò)散區(qū)和襯底之間的PN結(jié)上總存在反向漏電流,該漏電流與擴(kuò)散結(jié)濃度和面積有關(guān),從而造成一定的靜態(tài)功耗(參見(jiàn)圖4),其值可表示為:

式中,Vdd為電路的電源電壓值,Ileakaze為漏電流的值(見(jiàn)圖5)。

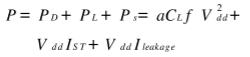

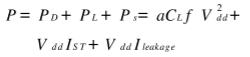

通過(guò)以上討論,可以得到電路的總功耗為:

式中,占主要地位的是PD,它主要取決于三個(gè)參數(shù):負(fù)載電容、時(shí)鐘頻率和電源電壓。隨著CMOS集成電路尺寸的減小,柵電容和電源電壓也相應(yīng)減小,當(dāng)門(mén)數(shù)固定、時(shí)鐘頻率提高時(shí),由于功耗近似正比于頻率和負(fù)載電容的一次方,而正比于電源電壓的二次方,所以整個(gè)電路功耗將減小。

圖4CMOS電路的靜態(tài)功耗

圖5CMOS電路的漏電流

2.低功耗設(shè)計(jì)方法

2.1工藝調(diào)整的影響

隨著工藝的發(fā)展,溝道長(zhǎng)度不斷減小,金屬層不斷增加,對(duì)低功耗設(shè)計(jì)帶來(lái)一定的影響。作為電路設(shè)計(jì)者,不可能去改變工藝上的參數(shù),但是對(duì)這些工藝的了解有助于設(shè)計(jì)。

(1)Vr的優(yōu)化

隨著工藝的進(jìn)步和頻率的不斷提高,器件特征尺寸隨之減小,氧化層的厚度也相應(yīng)變薄,器件所能承受的電壓降低,使電源電壓減小,從而降低了功耗。由于電源電壓減小,閾值電壓Vr必須從先前的0.7~1.0V下降到0.~0.3V。但是,隨著Vr的減小,漏電流所產(chǎn)生的功耗在總功耗中所占的比例就有可能上升。

(2)工藝尺寸的減小

器件工藝尺寸的不斷減小對(duì)功耗的降低和電路速度的提高有著重要的影響。其中主要的一點(diǎn)是整個(gè)電容的減少,這將在一定程度上減少電路的功耗和延遲。柵電容和連線(xiàn)電容一般可以用下式表示:

式中,W為寬度,L為長(zhǎng)度,tox為氧化層厚度,Eαr為氧化層介電常數(shù)。

但是,金屬互連線(xiàn)的厚度幾乎沒(méi)有隨著工藝尺寸縮小而減小,所以金屬層和襯底的側(cè)壁電容變化不大。因此,電容的減小不如我們想象的那么明顯。

隨著器件工藝尺寸的減小,降低了電路的電源電壓,前面已分析過(guò)電路的功耗與Vdd近似成正比,所以功耗有明顯的下降。

(3)工藝制造的進(jìn)步

在現(xiàn)在先進(jìn)的工藝制造中,一些新技術(shù)的采用,例如金屬層的增加、允許通孔層疊等,都對(duì)降低功耗有一定的影響。

對(duì)于兩層金屬的工藝,在布線(xiàn)時(shí),由于上層金屬一般用于cell和cell之間的全局連接,所以一些cell內(nèi)部的信號(hào)線(xiàn)常用多晶硅連接。如果有兩層或更多的金屬層,就可以利用高層的金屬來(lái)進(jìn)行cell內(nèi)部的信號(hào)連線(xiàn)。對(duì)于各不同層的金屬來(lái)說(shuō),它們的單位電容值是隨層次的增高而降低的。因此,運(yùn)用多層金屬布線(xiàn)可以相對(duì)地減少電路的功耗。

通孔和通孔之間的距離在一定程度上決定了電路面積的大小,如果允許通孔的層疊,電路面積將有可能減少,同樣也減少了cell內(nèi)部和全局布線(xiàn)的金屬線(xiàn)的長(zhǎng)度。但是,相互間連線(xiàn)的耦合電容將有可能增加,就可能抵消先前的功耗降低。

2.2設(shè)計(jì)方法

(1)總線(xiàn)

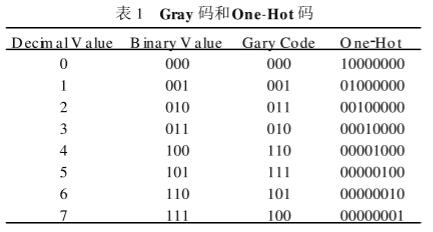

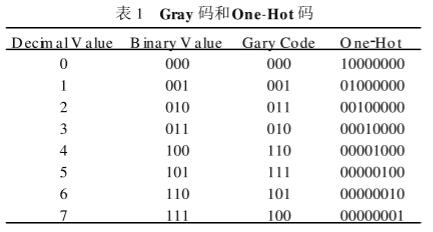

對(duì)某些電路的設(shè)計(jì)來(lái)說(shuō),它會(huì)包含相當(dāng)數(shù)量的總線(xiàn)。由于總線(xiàn)會(huì)帶來(lái)大負(fù)載、長(zhǎng)連線(xiàn)、大電阻等效應(yīng),所以,總線(xiàn)的功耗要占整個(gè)芯片總功耗的15%~20%。為了降低這一部分功耗,可以利用一些特定的編碼來(lái)減少信號(hào)的變化數(shù),以降低由數(shù)據(jù)傳輸而造成的功耗。一般可采用One-Hot(在一個(gè)二進(jìn)制數(shù)中,只允許一個(gè)數(shù)位不同于其它各數(shù)位的值)或Gray碼(任何兩個(gè)連續(xù)的數(shù)字,其對(duì)應(yīng)的二進(jìn)制碼只有一個(gè)位的數(shù)值不同,其余位數(shù)值均相同)在訪問(wèn)相鄰的兩個(gè)地址的內(nèi)容時(shí),其跳變次數(shù)比較少,這樣可以避免額外功耗的產(chǎn)生。(見(jiàn)表1)

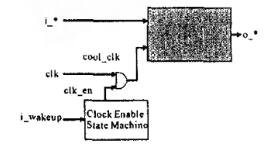

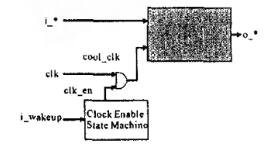

(2)門(mén)控時(shí)鐘

對(duì)于時(shí)序邏輯電路,時(shí)鐘樹(shù)消耗的功耗約為整個(gè)芯片功耗的15%~45%。為了減少這一部分功耗,可以采用門(mén)控時(shí)鐘(clockgating),使一些暫時(shí)不工作的器件處于非觸發(fā)狀態(tài),當(dāng)需要這些器件工作時(shí),可以用使能信號(hào)觸發(fā)它們,通過(guò)這一方法可以減少不必要的功耗。

圖6門(mén)控時(shí)鐘

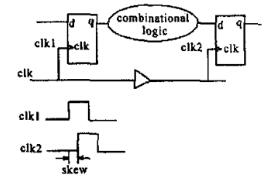

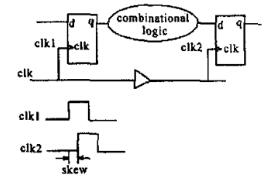

需要注意的是,門(mén)控時(shí)鐘信號(hào)應(yīng)置于相對(duì)較高的層次,而不是針對(duì)某個(gè)特定的觸發(fā)器。如果這樣的話(huà),會(huì)造成不必要的clockskew(時(shí)鐘之間的時(shí)間差,見(jiàn)圖7)

圖7時(shí)鐘之間的時(shí)間差

(3)閃變信號(hào)

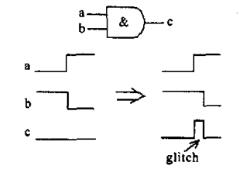

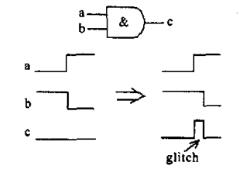

對(duì)于含有組合邏輯的電路來(lái)說(shuō),它的閃變信號(hào)(glitch)功耗將占整個(gè)芯片功耗的15%~20%。在靜態(tài)邏輯門(mén)電路中,輸出口或器件內(nèi)部接點(diǎn)的信號(hào)會(huì)在正確的邏輯值穩(wěn)定之前變化,這種不必要的信號(hào)變化將造成額外的功耗(見(jiàn)圖8)。一個(gè)兩輸入與門(mén),輸入信號(hào)分別由01→10,假定器件的門(mén)延時(shí)為0,則輸出端恒為0。由于輸入端信號(hào)到達(dá)的時(shí)間不同,就會(huì)出現(xiàn)多余的信號(hào)變化,信號(hào)的變化使a端開(kāi)關(guān)系數(shù)值增加,功耗隨之增大。

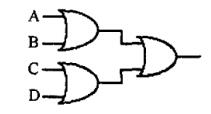

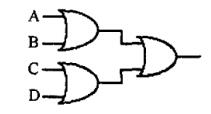

閃變信號(hào)的產(chǎn)生與路徑的長(zhǎng)度有一定的關(guān)系。一般來(lái)說(shuō),路徑越長(zhǎng),越易產(chǎn)生閃變信號(hào),原因之一是,不同的信號(hào)路徑長(zhǎng)度會(huì)造成信號(hào)到達(dá)時(shí)間的不同。因此在設(shè)計(jì)時(shí),應(yīng)盡量避免長(zhǎng)線(xiàn)的邏輯組合,或調(diào)整其結(jié)構(gòu),采用平衡樹(shù)結(jié)構(gòu)(見(jiàn)圖9)。此外,也可以通過(guò)其它方法來(lái)平衡電路的延遲,例如選擇不同驅(qū)動(dòng)能力的邏輯器件,或者在電路中插入buffer。但一般只有通路中的器件開(kāi)關(guān)頻率較高時(shí),才用這種方法來(lái)改善功耗問(wèn)題。

圖8閃變信號(hào)

圖9平衡樹(shù)結(jié)構(gòu)

(4)睡眠模式

睡眠模式(sleepmode)是一種可以用來(lái)降低功耗的可選方式。整個(gè)系統(tǒng)的動(dòng)作狀態(tài)處于被監(jiān)控的狀態(tài),如果系統(tǒng)或電路在某段預(yù)設(shè)的時(shí)間段內(nèi)處于閑置狀態(tài),那么整個(gè)系統(tǒng)或電路將自動(dòng)關(guān)閉。但是其輸入還是處于響應(yīng)狀態(tài),一旦有任何輸入信號(hào)被觸發(fā),整個(gè)系統(tǒng)或電路將被重新激活,回到正常的工作狀態(tài),這樣可以降低相應(yīng)的功耗。這種模式對(duì)需處于睡眠狀態(tài)時(shí)間較長(zhǎng)的器件比較有利,因?yàn)閺乃郀顟B(tài)到正常工作狀態(tài)的時(shí)間有時(shí)需要幾微秒,甚至幾毫秒,而且系統(tǒng)或電路在進(jìn)入睡眠狀態(tài)和恢復(fù)到正常工作狀態(tài)都會(huì)有額外的功耗。

3.低功耗設(shè)計(jì)工具

現(xiàn)在有許多低功耗設(shè)計(jì)的EDA工具。根據(jù)工具所使用的不同階段,可以把它們分為四類(lèi):晶體管級(jí)、門(mén)級(jí)、RTL級(jí)和行為級(jí)。

3.1晶體管級(jí)

晶體管級(jí)的功耗分析工具是以晶體管為基本器件來(lái)估算電路的功耗,這類(lèi)工具比較成熟、精確、易懂。但此時(shí)已處于設(shè)計(jì)的后期階段,沒(méi)法對(duì)設(shè)計(jì)作大量的修改。代表性的工具有Synopsys的Power-MillSPCE、Mentor的MarchPA等。

3.2門(mén)級(jí)

門(mén)級(jí)的功耗分析工具是以邏輯門(mén)為基本器件來(lái)估算電路的功耗。盡管這類(lèi)工具不如晶體管級(jí)功耗分析工具精確,但是由邏輯門(mén)表示的電路比由晶體管表示的電路更易懂。代表性的工具有Synopsys的PowerCompiler,它可以重新優(yōu)化設(shè)計(jì),滿(mǎn)足功耗的要求。

3.3RIL級(jí)

RTL級(jí)的功耗分析工具是以RTL器件為基本器件來(lái)估算電路的功耗。由于它處于設(shè)計(jì)的前端,所以這類(lèi)工具對(duì)整個(gè)電路設(shè)計(jì)的功耗特性有著重要的影響。它們的速度較前兩者快,容量較前兩者大,但精確度相對(duì)較低。此外,這一類(lèi)工具可有效地估算由門(mén)控時(shí)鐘引起的功耗。

3.4行為級(jí)

目前行為級(jí)的功耗分析工具還處于研發(fā)階段。

總結(jié)

以上就是CMOS集成電路低功耗的設(shè)計(jì)方法介紹了。CMOS集成電路可在較廣泛的電源電壓范圍內(nèi)工作,便于與其他電路接口;并且速度快,門(mén)延遲時(shí)間達(dá)納秒級(jí);在模擬電路中應(yīng)用,其性能比NMOS電路好;與NMOS電路相比,集成度稍低。

〈烜芯微/XXW〉專(zhuān)業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷(xiāo)省20%,上萬(wàn)家電路電器生產(chǎn)企業(yè)選用,專(zhuān)業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷(xiāo)售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

聯(lián)系號(hào)碼:18923864027(同微信)

QQ:709211280