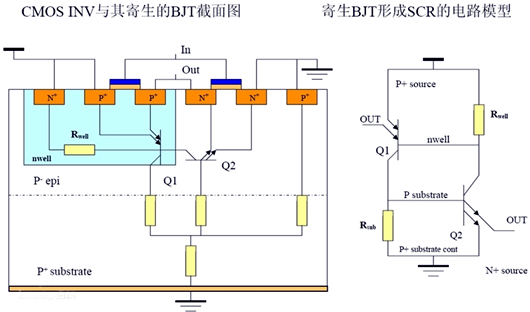

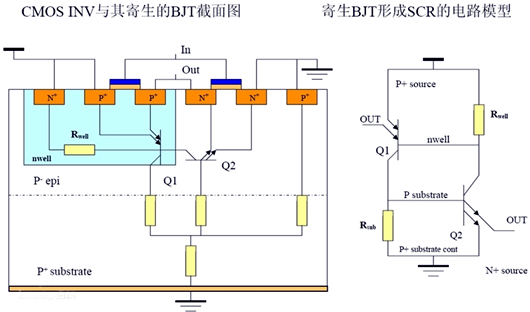

CMOS電路中,存在寄生的三極管PNPN,它們相互影響在VDD與GND間產生一低阻通路,形成大電流,燒壞芯片這就是閂鎖效應。

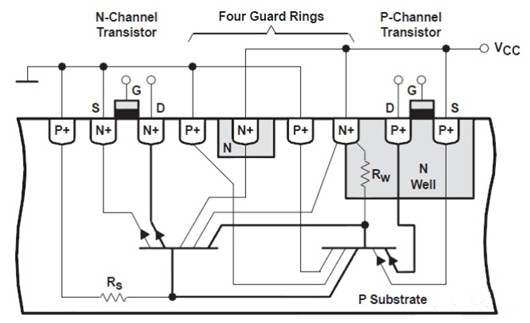

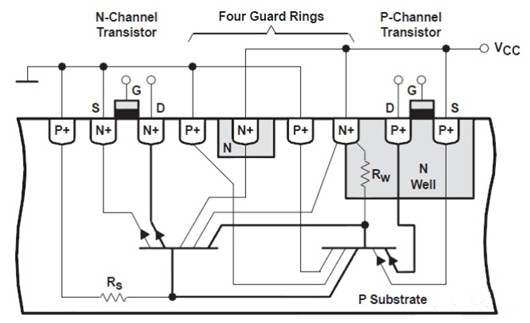

閂鎖效應是CMOS工藝所特有的寄生效應,嚴重會導致電路的失效,甚至燒毀芯片。閂鎖效應是由NMOS的有源區(qū)、P襯底、N阱、PMOS的有源區(qū)構成的n-p-n-p結構產生的,當其中一個三極管正偏時,就會構成正反饋形成閂鎖。避免閂鎖的方法就是要減小襯底和N阱的寄生電阻,使寄生的三極管不會處于正偏狀態(tài)。

靜電是一種看不見的破壞力,會對電子元器件產生影響。ESD 和相關的電壓瞬變都會引起閂鎖效應(latch-up),是半導體器件失效的主要原因之一。

如果有一個強電場施加在器件結構中的氧化物薄膜上,則該氧化物薄膜就會因介質擊穿而損壞。很細的金屬化跡線會由于大電流而損壞,并會由于浪涌電流造成的過熱而形成開路。這就是所謂的“閂鎖效應”。在閂鎖情況下,器件在電源與地之間形成短路,造成大電流、EOS(電過載)和器件損壞。

Latch up閂鎖效應觸發(fā)原因:

1. 芯片一開始工作時VDD變化導致nwell和P substrate間寄生電容中產生足夠的電流,當VDD變化率大到一定地步,將會引起Latch up。

2. 當I/O信號變換超過VDD-GND范圍,會有較大電流產生,也會觸發(fā)Latch up

3. ESD靜電泄放時,會從保護電路中引入載流子到阱和襯底中,也會觸發(fā)Latch up

4. 負載過大,VDD或GND突變時也可能會觸發(fā)Latch up

5. 阱側面漏電流過大,也會觸發(fā)Latch up

Latch-up產生機制和抑制方法:

Latch-up產生機制

1.輸入或輸出電壓(I/O的信號)高于VDD電壓,芯片產生大電流,導致latch-up;

2.ESD靜電加壓,可能會從保護電路中引入少量帶電載流子到阱或襯底中,導致latch-up;

Latch-up抑制方法

1.保持低于芯片的絕對最大額定值。

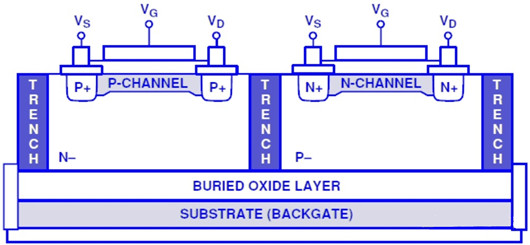

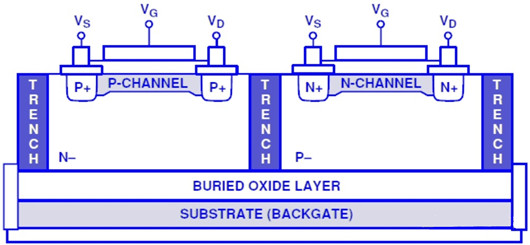

2.使用氧化物隔離槽(oxide trench)和掩埋氧化物(buried oxide)層隔離NMOS和PMOS器件:

3.如果不能使用oxide trench,可以使用guard rings。多子GuardRing : P+ Ring環(huán)繞NMOS并接GND; N+ Ring環(huán)接PMOS并接VDD。使用多子保護環(huán)可以降低Rwell和Rsub的阻值,且可以阻止多數(shù)載流子到基極。

少子GuardRing : 制作在N阱中的N+ Ring環(huán)繞NMOS并接VDD; P+ Ring環(huán)繞PMOS并接GND。 使用少子保護環(huán)可以減少因為少子注入到阱或襯底引發(fā)的閂鎖。

4.減小正反饋環(huán)路的增益。減小寄生晶體管的放大倍數(shù)和Rw/Rs阻值都可以有效降低環(huán)路增益。增加阱和襯底摻雜濃度以降低Rwell和Rsub, 例如,使用逆向摻雜阱。使NMOS和PMOS保持足夠的間距來降低引發(fā)SCR的可能。Sub接觸孔和Well接觸孔應盡量靠近源區(qū)。以降低Rwell和Rsub的阻值。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經理給您精準的報價以及產品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280