在電路設計中,常常會出現(xiàn)發(fā)送接收兩方的信號電平不匹配的情況,例如在I2C bus上,處理器電平一般是1.8V,但EEPROM則一般還是3.3V。

在這種情況發(fā)生的時候,邏輯上有兩種解決方法: 1. 調(diào)整某一方的電平使其匹配 2. 將兩方芯片的高電平輸出解耦,通過中間器件使其正常工作。

兩種解決方法

調(diào)整某一方的電平使其匹配

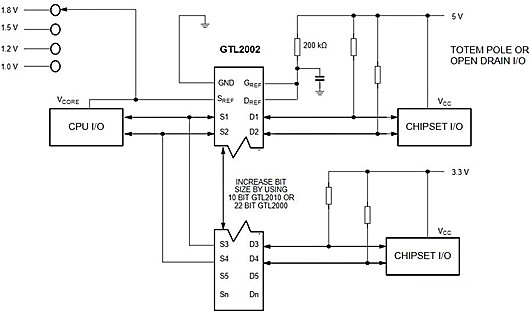

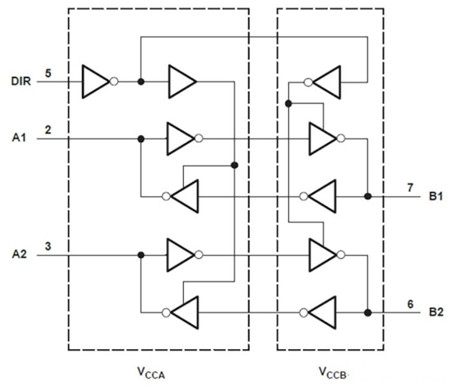

對于一般的設計或者常規(guī)思路,調(diào)整電平是最簡單的,無非增加一個電平轉(zhuǎn)換芯片,一種通用的電平轉(zhuǎn)換芯片如下,只需要做好reference voltage與input signal voltage的匹配,其他的芯片內(nèi)部的邏輯電路就可以完成了。

在這種芯片內(nèi)部,一般也是幾個邏輯器件,只是將某一方向的最后一個或者兩個管子的Vin換成了對應的輸出而已。這本質(zhì)上還是第二種方法的應用。

高電平輸出解耦

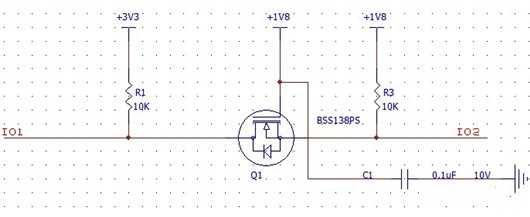

說起來高大上,輸出解耦,其實就是一個三極管隔離電路,只是這個電路具體細節(jié)分析起來相對麻煩一點,并且對于使用的MOS管參數(shù)也要仔細分析。

比如下圖電路。 首先查一下Q1的參數(shù), Vgsth = 0.9V.min Vsd = 1.1V.max

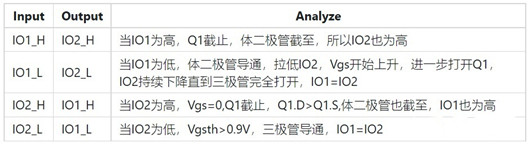

對于輸入輸出,有四種情況:

要點

對于Q1,Vgs在靜態(tài)要等于0V,最好Gate和Source使用同源電平,Vsd在靜態(tài)要小于手冊里Vsd的值,否則會造成管子打開關(guān)不上的情況。靜態(tài)狀態(tài)下Vs<Vd。

有種設計會使用體二極管的單向?qū)ǚ乐孤╇?,這種情況下也必須滿足要點1的要求;當漏電與體二極管方向發(fā)生沖突的時候,要優(yōu)先滿足體二極管方向。

C1是為了上電瞬間打開管子的曲線平滑一些,同時讓輸入輸出電平穩(wěn)定后再提供Gate端電平。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280