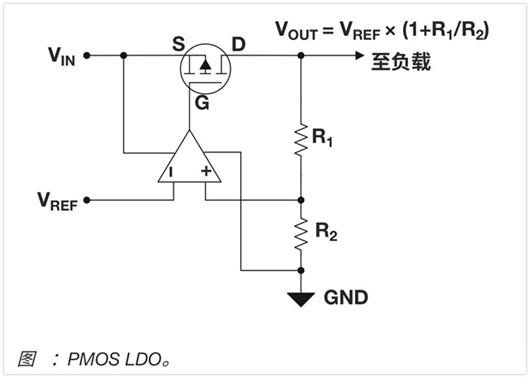

PMOS LDO

圖所示為 PMOS LDO 架構(gòu)。為調(diào)節(jié)所需的輸出電壓,反饋回路將控制漏-源極電阻 RDS。隨著 VIN 逐漸接近 VOUT(nom),誤差放大器將驅(qū)動(dòng)?xùn)?源極電壓 VGS 負(fù)向增大,以減小 RDS,從而保持穩(wěn)壓。

但是,在特定的點(diǎn),誤差放大器輸出將在接地端達(dá)到飽和狀態(tài),無(wú)法驅(qū)動(dòng) VGS 進(jìn)一步負(fù)向增大。RDS 已達(dá)到其最小值。將此 RDS 值與輸出電流 IOUT 相乘,將得到壓降電壓。

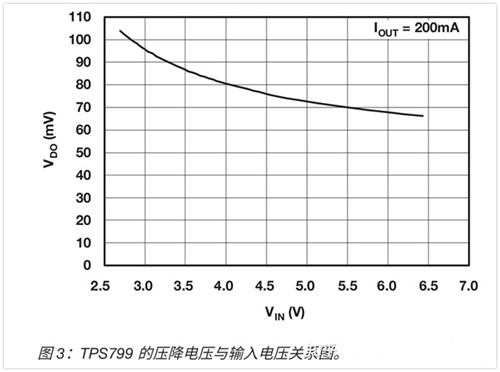

請(qǐng)記住,隨著 VGS 負(fù)向增大,能達(dá)到的 RDS 值越低。通過(guò)提升輸入電壓,可以使VGS 值負(fù)向增大。因此,PMOS 架構(gòu)在較高的輸出電壓下具有較低的壓降。下圖展示了此特性。

如圖所示,TPS799 的壓降電壓隨輸入電壓(也適用于輸出電壓)增大而降低。這是因?yàn)殡S著輸入電壓升高 VGS會(huì)負(fù)向增大。

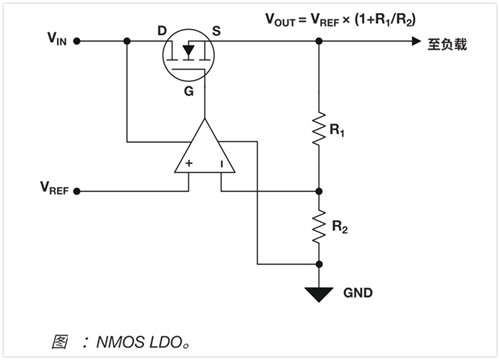

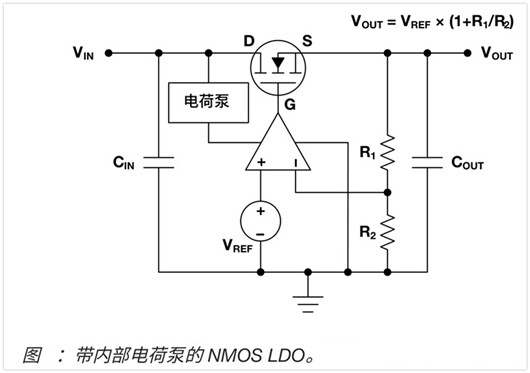

NMOS LDO

NMOS 架構(gòu)如圖所示,反饋回路仍然控制 RDS。但是,隨著VIN 接近 VOUT(nom),誤差放大器將增大 VGS 以降低 RDS,從而保持穩(wěn)壓。

在特定的點(diǎn),VGS 無(wú)法再升高,因?yàn)檎`差放大器輸出在電源電壓 VIN 下將達(dá)到飽和狀態(tài)。達(dá)到此狀態(tài)時(shí),RDS處于最小值。將此值與輸出電流 IOUT 相乘,會(huì)獲得壓降電壓。

不過(guò)這也會(huì)產(chǎn)生問(wèn)題,因?yàn)檎`差放大器輸出在 VIN 處達(dá)到飽和狀態(tài),隨著 VIN 接近 VOUT(nom),VGS 也會(huì)降低。這有助于防止出現(xiàn)超低壓降。

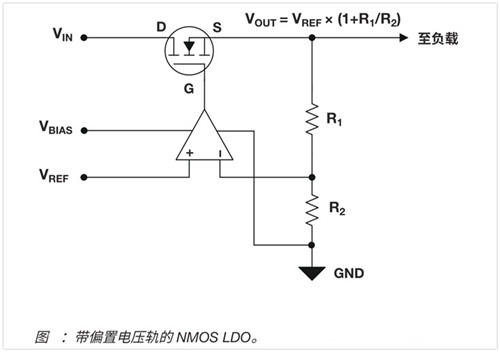

偏置 LDO

很多 NMOS LDO 都采用輔助電壓軌,即偏置電壓 VBIAS,如圖所示。

電荷泵將提升 VIN,以便誤差放大器在缺少外部 VBIAS 電壓軌的情況下仍可以生成更大的 VGS 值。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷(xiāo)省20%,上萬(wàn)家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷(xiāo)售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹

聯(lián)系號(hào)碼:18923864027(同微信)

QQ:709211280