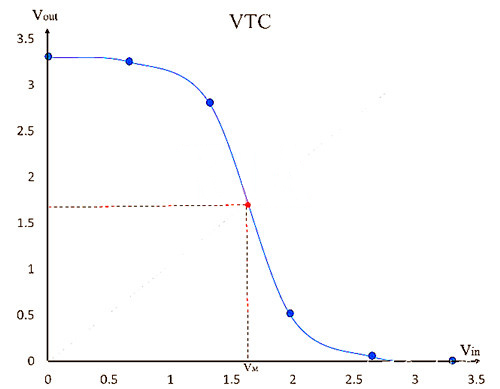

CMOS反相器的開關閾值Vm定義為當輸入電壓與輸出電壓相等時的電壓值,即圖1紅點處

圖1 CMOS反相器的電壓傳輸特性(VTC)曲線

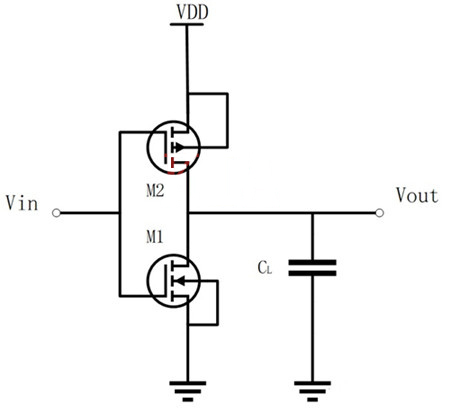

圖2 靜態(tài)CMOS反相器晶體管級電路

對流過PMOS與NMOS的電流列方程就可求出Vm,而流過MOS管的電流受MOS管的工作區(qū)域的影響,下面是對MOS的工作區(qū)域的簡單介紹:

MOS管的導通條件是|Vgs| > |Vt|,決定其飽和導通還是線性導通需要考慮漏源電壓:

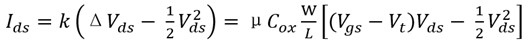

當|Vds| < |Vgs - Vt|時,MOS管線性導通,漏電流為:

k=μCox(W/L)為工藝參數(shù),Δ=Vgs - Vt為過驅(qū)動電壓

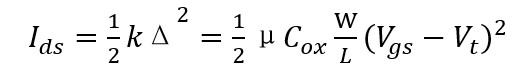

當|Vds| > |Vgs - Vt|時,MOS管飽和導通,漏電流為:

對于短溝道器件來說,|Vds|增大到一定程度會出現(xiàn)載流子漂移速度飽和,此時的飽和漏電流的表達式為:

Vdsat為飽和漏極電壓

接下來分析CMOS反相器中PMOS與NMOS在Vin=Vout=Vm時的工作區(qū)域:

Ⅰ. PMOS:

|Vgsp| = |Vm-Vdd| > |Vtp| 且 |Vdsp| = |Vm-Vdd| = |Vgsp| >|Vgsp-Vtp|,故PMOS飽和導通

Ⅱ. NMOS:

Vgsn = Vm > Vtn 且 Vdsn = Vm = Vgsn >Vgsn-Vtn,故NMOS飽和導通

PMOS與NMOS都處于飽和導通,電流由Vdd流向地,流經(jīng)PMOS的電流為-Idsp,流經(jīng)NMOS的電流為Idsn,所以Idsp+Idsn=0...式①

現(xiàn)如今的半導體器件大多是納米級別的,屬于短溝道器件,所以在求解Vm時使用速度飽和漏電流公式,聯(lián)立式①與MOS管的飽和漏電流公式得:

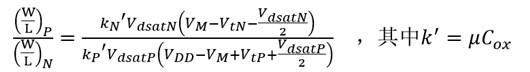

式②,k為工藝參數(shù), Vdsat為飽和漏極電流

解得

注:Vdsat是漏極飽和電壓,vdsat是載流子的漂移飽和速度

由式②亦可解得在給定Vm的條件下PMOS與NMOS的寬長比之比:

在設計CMOS反相器時,將想要得到的Vm值代入式③可算得PMOS與NMOS的寬長比之比。

注:選擇的Vm值要使NMOS與PMOS同時處于速度飽和才可使用式③

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280