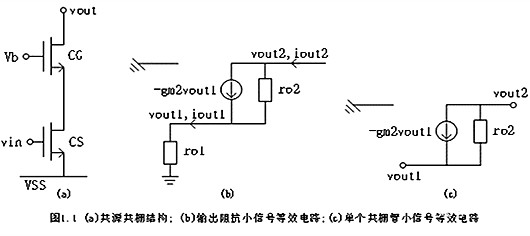

共源共柵結(jié)構(gòu)(cascode structure, CSCG)具有很多特點,在CMOS電路中很常見,以NMOS為例,如圖1.1(a)所示。

共源共柵結(jié)構(gòu)最大的特點就是輸出阻抗大。 共源管下標為1,共柵管下標為2,單個共源管的輸出阻抗為ro1,而共源共柵結(jié)構(gòu)的輸出阻抗近似為gm2ro1ro2。

怎么理解共源共柵結(jié)構(gòu)的輸出阻抗比單個共源管放大了gm2ro2倍?

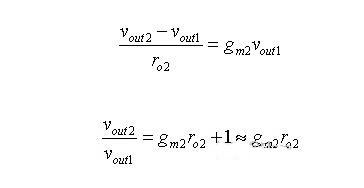

在圖1.1(c)中,單個共柵管的增益求解如下:

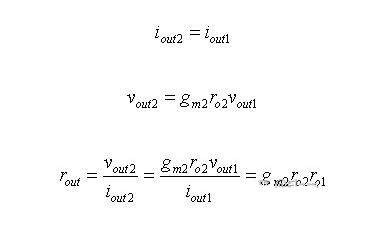

在圖1.1(b)中,輸出阻抗求解過程如下:

由于共源共柵結(jié)構(gòu)的輸出阻抗大這個特點,比單個共源管放大了gm2ro2倍,在高增益的運放中,共源共柵結(jié)構(gòu)經(jīng)常作為輸入管和輸出負載管以提高電壓增益。

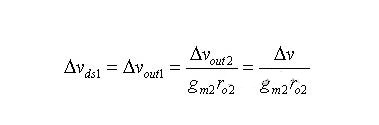

共源共柵管的另一個特點是共源管的源漏電壓vds1對輸出電壓不敏感,當輸出電壓變化Δv時,Δvds1可表示為:

因此,即便共源共柵結(jié)構(gòu)的輸出負載變化很大,只要保證共柵管仍工作在飽和區(qū)且有比較大的電壓增益,共源管的源漏電壓vds1的變化也很小。這一特點使得共源共柵結(jié)構(gòu)經(jīng)常被應用在電流鏡中。

折疊共源共柵結(jié)構(gòu)

在共源共柵結(jié)構(gòu),共源管將輸入電壓轉(zhuǎn)換成電流,該電流作為共柵管的輸入。同類型的晶體管的共源共柵結(jié)構(gòu)串接即可。不同類型管需要外加偏置電流折疊形成,因此折疊共源共柵一定是PN成對地用。

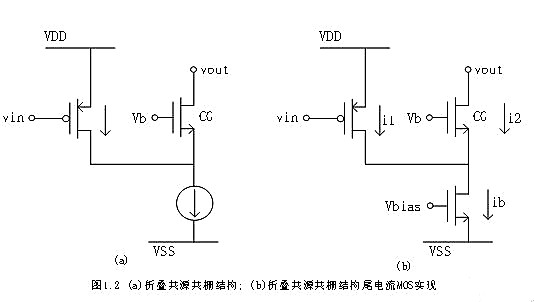

如果想把圖1.1(a)所示的共源共柵結(jié)構(gòu)改成折疊結(jié)構(gòu),則應把輸入管由NMOS管改成PMOS管,同時增加尾電流源,如圖1.2(a)所示。

尾電流源通過MOS實現(xiàn),一般的PMOS管作為輸入的折疊共源共柵結(jié)構(gòu)如圖1.2(b)所示,其中尾電流ib=i1+i2。

隨著電源電壓越來越低,在運放中,更經(jīng)常使用折疊共源共柵結(jié)構(gòu)作為輸入管。折疊共源共柵結(jié)構(gòu)的優(yōu)缺點:輸出擺幅大些,輸入輸出可以短接,較大的功耗,較低的增益,較低的極點頻率,較高的噪聲。

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹

聯(lián)系號碼:18923864027(同微信)

QQ:709211280