眾所周知,在電路板的電路設(shè)計(jì)階段就進(jìn)行電磁兼容性設(shè)計(jì)是非常重要的,而設(shè)備和系統(tǒng)向外部環(huán)境發(fā)射的騷擾電平是通過(guò)傳導(dǎo)和輻射的途徑形成的。傳統(tǒng)的設(shè)計(jì)方法是用屏蔽、濾波和接地解決電纜口和殼體帶來(lái)的EMC問(wèn)題。但是大多數(shù)干擾是在電路板上產(chǎn)生的,因此,在電路板的電路設(shè)計(jì)階段,就應(yīng)該考慮電磁兼容設(shè)計(jì)。

1.差模電流和共模電流

1.1差模發(fā)射和共模發(fā)射

任何電路都存在共模(CM)和差模(DM)電流。共模電流和差模電流都決定了傳播的RF能量的大小。在兩者之間有較大的區(qū)別。如果給定一對(duì)導(dǎo)線或走線,一個(gè)返回參考源,那么這兩種模式中的一種將會(huì)存在。一般來(lái)說(shuō),差分模式信號(hào)攜帶數(shù)據(jù)或有用信息。共模模式是差分模式電流的負(fù)面效果,并對(duì)電磁兼容性是最麻煩的。通常把線線的發(fā)射定義為差模發(fā)射。把線-地的發(fā)射定義為共模發(fā)射。

由閉合回路產(chǎn)生的最大的場(chǎng)強(qiáng)是:

式中:E—最大輻射場(chǎng)強(qiáng)( μV/m);

r—回路和測(cè)量天線之間的距離( m);

F—頻率(MHz);

Is—電流( mA );

A—回路面積( c㎡)。

由式(1)可以看出,場(chǎng)強(qiáng)和回路面積成正比。

為減小差模發(fā)射電平,除減小源電流外,應(yīng)該減小環(huán)電路的面積。

共模輻射是由于在電路設(shè)計(jì)之外的電壓降造成的,這種電壓降致使電路的一些接地部分的電壓比真實(shí)的參考地面高。與受影響的接地系統(tǒng)相連的電纜就作為天線,輻射共模的場(chǎng)分量。遠(yuǎn)場(chǎng)分量可用下式描述:

式中:K—發(fā)射系數(shù);

I—共模電流(A);

l—線的長(zhǎng)度(m);

f—發(fā)射的頻率(MHz);

r—距離( m)。

由式(2)可以看出場(chǎng)強(qiáng)和電纜的長(zhǎng)度成正比,減小共模發(fā)射應(yīng)降低共模電流和縮短電纜線的長(zhǎng)度。

1.2差模和共模的轉(zhuǎn)變

當(dāng)存在兩個(gè)具有不同阻抗的信號(hào)線(或?qū)w)時(shí)差模和共模就可以互相轉(zhuǎn)變。這些阻抗主要由與走線(或內(nèi)在電纜)的物理布線相關(guān)的導(dǎo)線或梳狀電容和電感決定。對(duì)于大部分的電路板布線來(lái)說(shuō),主要是控制網(wǎng)絡(luò)中的寄生電容和電感,并使其最小,從而避免差模和共模的產(chǎn)生。

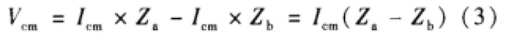

如圖1中差模電流Idm是需要的信號(hào),它要流經(jīng)負(fù)載RL。共模電流Icm不直接經(jīng)過(guò)RL,它將經(jīng)過(guò)Za和Zb,然后通過(guò)回流結(jié)構(gòu)返回。阻抗Za和Zb并不是物理元件,它們是網(wǎng)絡(luò)中存在著的寄生電容或寄生電感的轉(zhuǎn)移阻抗。如果Za和Zb不等電壓差將正比于阻抗差。

所以對(duì)外界敏感的電路必須通過(guò)某種方式達(dá)到平衡,使得每個(gè)導(dǎo)體的引線或梳狀電容以及寄生電容相等。

圖1 差模轉(zhuǎn)共模

1.3差模和共模干擾的抑制

抑制電路板內(nèi)的差模和共模電流,以及由此引起的RF干擾,最基本的就是通量抵消法或通量最小化。電流在走線中流動(dòng)產(chǎn)生磁力線,這些磁力線產(chǎn)生電場(chǎng),這兩種場(chǎng)都會(huì)輻射RF能量。如果我們將磁力線抵消或減小到最小,那么將不會(huì)存在RF能量,也就抑制了干擾。主要采取以下幾點(diǎn):

(1)安排時(shí)鐘走線臨近接地平面(多層板)接地櫥格或接地線(雙面板或單面板);

(2)仔細(xì)選擇邏輯系列器件以使元件輻射分離出的RF能量最小;

(3)通過(guò)減小時(shí)鐘產(chǎn)生電路中的RF驅(qū)動(dòng)電壓來(lái)減小走線中的RF電流;

(4)減小電源和接地結(jié)構(gòu)中的噪音;

(5)當(dāng)有外部VO電纜提供時(shí)正確應(yīng)用旁路電容;

(6)為那些輻射大量?jī)?nèi)部共模RF能量的元件提供接地散熱器;

(7)在電路板布局和布線時(shí)盡量使電路達(dá)到某種平衡。

2.串?dāng)_及串?dāng)_的抑制

2.1串?dāng)_

串?dāng)_是電路板設(shè)計(jì)中的重要部分之一,在設(shè)計(jì)的任一環(huán)節(jié)都需要考慮。串?dāng)_是指走線、導(dǎo)線、走線和導(dǎo)線,電纜束元件及其它易受電磁干擾的電子元件之間的不希望有的電磁耦合。

串?dāng)_是EMI傳播的主要途徑,會(huì)引起走線間干擾。串?dāng)_包括電容耦合和電感耦合。電容耦合通常是因?yàn)樽呔€位于另一走線上方或參考層上方。電感耦合通常是因?yàn)槲锢砦恢蒙鲜纸咏淖呔€。對(duì)于并行走線,串?dāng)_有兩種方式:前向和后向。在 PCB中,后向串?dāng)_通常比前向串?dāng)_更值得考慮。電路中源與受干擾走線間阻抗越大產(chǎn)生的串?dāng)_電平越高。電感串?dāng)_可以通過(guò)增加走線與傳輸線或?qū)Ь€間的邊到邊間隔或最小化走線距離參考層上的高度而得到控制。

2.2串?dāng)_的抑制

為了抑制印刷電路板導(dǎo)線之間的串?dāng)_,在設(shè)計(jì)布線時(shí)應(yīng)注意以下幾條:

(1)根據(jù)電路的功能分類(lèi)邏輯器件,合理布局電路板;

(2)盡量避免長(zhǎng)距離的平行走線,盡可能拉開(kāi)線與線之間的距離以最小化電感耦合,信號(hào)線與地線及電源線盡可能不交叉;

(3)在一些對(duì)于敏感的信號(hào)線之間,設(shè)計(jì)一根接地印刷線,可以有效地抑制串?dāng)_;

(4)元件要遠(yuǎn)離Vo互連接口及其它易受數(shù)據(jù)干擾及耦合影響的區(qū)域;

(5)降低信號(hào)到地的參考距離;

(6)降低走線阻抗和信號(hào)驅(qū)動(dòng)電平;

(7)把高噪聲發(fā)射體(時(shí)鐘、VO、高速互連等)分割或隔離在不同的區(qū)域;

(8)對(duì)時(shí)鐘周期走線,差分走線、復(fù)位線等一些關(guān)鍵的系統(tǒng)走線強(qiáng)制使用3W原則(走線間的距離間隔必須是單一走線寬度的3倍)。

3.數(shù)字信號(hào)頻譜分析

3.1數(shù)字信號(hào)

數(shù)字信號(hào)的特點(diǎn)是方波,方波信號(hào)是由基波和大量諧波正弦(或余弦)信號(hào)構(gòu)成的,這可由傅立葉變換得到其頻域波形,因此,脈沖重復(fù)周期越短,其重復(fù)頻率越高,諧波頻率也越高。理論上方波的上升時(shí)間為零,則諧波含量是無(wú)窮的。但實(shí)際上是梯形波形,有一定的上升沿和下降沿。

3.2脈沖的時(shí)域/頻域變換(傅立葉變換)

通過(guò)傅立葉變換,矩形脈沖可分解為各次余弦(或正弦)波。

其表達(dá)式:

式中:An—各次余弦波形的幅度;

n—諧波次數(shù);

w—角頻率。

4.去耦與接地

4.1電路的去耦設(shè)計(jì)

電感和電容組成的低通濾波器,可濾掉高頻段干擾信號(hào)。由于導(dǎo)線寄生電感的影響,會(huì)使供電的速度變慢,使驅(qū)動(dòng)器件輸出電流下降,合理放置去耦電容,在通斷瞬間,利用電感和電容的儲(chǔ)能作用,給器件提供電流。在直流電源回路中,負(fù)載的變化會(huì)引起電源噪聲。配置去耦電容可以抑制因負(fù)載變化而產(chǎn)生的噪聲,配置原則為:印刷電路板的電源輸人端跨接一個(gè)10uF ~100uF的電解電容器,如果印刷電路板的位置允許,采用100uF以上的電解電容器的抗干擾效果會(huì)更好;對(duì)于耗電較大的集成電路芯片,也應(yīng)在電源端安裝合適的電解電容。小電容能為集成電路塊提供高速電流,在器件輸出端電壓跳變時(shí),它能高速充電,為器件提供充電電流。

4.2電路的接地設(shè)計(jì)

在電子設(shè)備中,接地是控制干擾的重要方法。如能將接地和屏蔽正確結(jié)合起來(lái)使用,可解決大部分干擾問(wèn)題。

當(dāng)電路板上頻率小于1 MHz時(shí),由于布線和元件之間的電磁感應(yīng)影響很小,而接地電路形成的環(huán)流產(chǎn)生的干擾較大,所以要采用一點(diǎn)接地,使其不形成回路;當(dāng)信號(hào)頻率高于100MHz時(shí),由于布線的電感效應(yīng)明顯,地線阻抗明顯增加,此時(shí)接地電流形成的環(huán)流不再是主要問(wèn)題了,所以應(yīng)采用多點(diǎn)接地,盡量降低地線阻抗。但是,當(dāng)工作頻率在1MHz~10 MHz之間時(shí),如果采用一點(diǎn)接地,其地線長(zhǎng)度不應(yīng)超過(guò)波長(zhǎng)的1/20,否則應(yīng)采用多點(diǎn)接地。當(dāng)一個(gè)系統(tǒng)中既有低頻電路又有高頻電路時(shí),應(yīng)采用混合接地的原則。系統(tǒng)內(nèi)的低頻部分采用單點(diǎn)接地,而高頻部分采用多點(diǎn)接地。

電路板上既有數(shù)字電路,又有模擬電路,應(yīng)使它們盡量分開(kāi)布線,而兩者的地線應(yīng)分別與電源端地線相連。另外還需盡量加大模擬電路引出端的接地面積。如果地線很細(xì),則地線電阻將會(huì)較大,造成接地電位隨電流的變化而變化,致使信號(hào)電平不穩(wěn),導(dǎo)致電路的抗干擾能力下降,因此應(yīng)將接地線盡量加粗。在布線空間允許的情況下,要保證主要地線的寬度至少在2 mm 以上,元件引腳上的接地線直徑應(yīng)該在1.5 mm左右。

對(duì)于只有數(shù)字電路組成的印刷板的地線系統(tǒng),將接地線做成閉合環(huán)路,可以明顯提高抗干擾能力。其原因在于:印制電路板上有很多的元件時(shí),因受接地線粗細(xì)的限制,會(huì)在接地上產(chǎn)生較大的電位差,引起抗干擾能力下降。若將接地結(jié)構(gòu)構(gòu)成環(huán)路,則會(huì)縮小電位差值,提高電子設(shè)備的抗干擾能力。

電源線的布置要根據(jù)電流的大小盡量加粗走線寬度。在布線工作的最后,用地線將電路板沒(méi)有走線的地方鋪滿(大面積)。

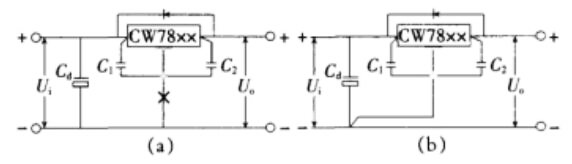

在接地時(shí)還需要避免共阻抗路徑,如圖3所示穩(wěn)壓器電路的“調(diào)整端的取樣點(diǎn)”或“公共點(diǎn)”,千萬(wàn)不能接在有負(fù)載電流流過(guò)的輸出線和公共地線上如圖2(a)所示,應(yīng)從管腳根部單獨(dú)另外用引線引出如圖2(b)所示。

圖2 避免共阻抗路徑

這是由于集成穩(wěn)壓電路的取樣放大器的增益很高,調(diào)整端和公共端每1mV的電壓變化,都會(huì)被放大到輸出端進(jìn)行逆向跟蹤調(diào)整,反映的現(xiàn)象就是輸出不穩(wěn)定,直觀的反映就是電源的紋波、PP值等指標(biāo)超差。

5.電路布局元器件安裝位置和合理布線

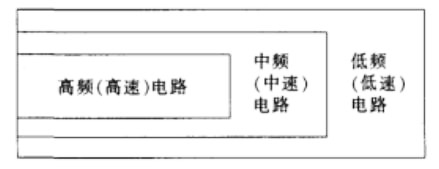

電路布局直接影響電磁干擾和抗干擾強(qiáng)度。合理的布局不僅可以使電路的效率得到提高,更能使整個(gè)系統(tǒng)的EMC得到改善。單元電路工作頻率越高,速度也就越快,信號(hào)頻譜也就越豐富,高頻分量比例越大,對(duì)外干擾也就越強(qiáng)。從頻率而言是先高頻,再中頻電路,最后低頻電路;而從邏輯速度而言,是先高速電路,再中速電路,最后低速電路,如圖3所示。

圖3 按頻率進(jìn)行的布局

除按工作頻率(或速度)進(jìn)行分組外,也可按照其功能和類(lèi)型進(jìn)行分組,例如,既存在數(shù)字電路,又存在模擬電路的電路板,可按工作電壓和頻率分組布局,在給定電路系列或電源電壓時(shí),可按功能對(duì)器件分組。

結(jié)束語(yǔ)

以上就是電路板的電磁兼容設(shè)計(jì)介紹了。本文主要分析了共模和差模干擾、串?dāng)_產(chǎn)生的機(jī)理及抑制措施。在實(shí)際的設(shè)計(jì)過(guò)程中,電磁兼容問(wèn)題依然是一個(gè)很復(fù)雜的問(wèn)題,需要從多個(gè)角度去考慮與分析,以得到滿意的設(shè)計(jì)結(jié)果。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷(xiāo)省20%,上萬(wàn)家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷(xiāo)售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹