傳統(tǒng)數(shù)字濾波器硬件的實(shí)現(xiàn)主要采用專用集成電路(ASIC)和數(shù)字信號(hào)處理器(DSP)來實(shí)現(xiàn)。FPGA內(nèi)部的功能塊中采用了SRAM的查找表(lo-ok up table,LUT)結(jié)構(gòu),這種結(jié)構(gòu)特別適用于并行處理結(jié)構(gòu),相對(duì)于傳統(tǒng)方法來說,其并行度和擴(kuò)展性都很好,它逐漸成為構(gòu)造可編程高性能算法結(jié)構(gòu)的新選擇。

分布式算法是一種適合FPGA設(shè)計(jì)的乘加運(yùn)算,由于FPGA中硬件乘法器資源有限,直接應(yīng)運(yùn)乘法會(huì)消耗大量的資源。本文利用了豐富的存儲(chǔ)器資源進(jìn)行查找表運(yùn)算,設(shè)計(jì)了一種基于分布式算法低通FIR濾波器;利用線性相位FIR濾波器的對(duì)稱性減小了硬件規(guī)模,采用了分割查找表技術(shù),節(jié)省了FPGA硬件資源,并采用并行分布式算法結(jié)構(gòu)和流水線技術(shù)提高了濾波器的速度,在FPGA上實(shí)現(xiàn)了該濾波器。

1.分布式的濾波器算法

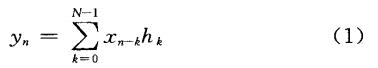

FIR濾波器突出的特點(diǎn)是單位取樣響應(yīng)h(n)僅有有限個(gè)非零值。對(duì)于一個(gè)N階的FIR濾波器形式如下:

在許多數(shù)字信號(hào)處理應(yīng)用領(lǐng)域中,在技術(shù)上是不需要通用的乘法算法的。對(duì)于本系統(tǒng)可以通過Matlab中的fdatool工具根據(jù)設(shè)計(jì)要求設(shè)計(jì)出濾波器的系統(tǒng)函數(shù)h(n),那么乘積項(xiàng)h(k)×x(n-k)就變成了2個(gè)常數(shù)的乘法。無符號(hào)數(shù)的分布式算法和有符號(hào)數(shù)的分布式算法是分布式算法在FIR濾波器中的2種典型算法。

1.1無符號(hào)數(shù)的分布式算法設(shè)計(jì)

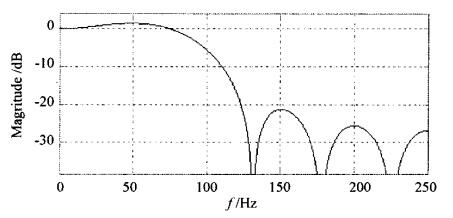

由于FPGA為并行處理結(jié)構(gòu),所以假設(shè)x(n-k)數(shù)據(jù)寬度為L b,則由式(1)可表示為:

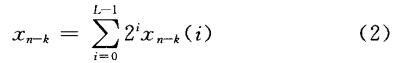

由式(1)、式(2)可以得到:

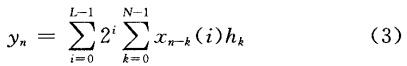

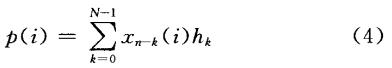

假設(shè):

則式(1)可以表示為:

1.2有符號(hào)數(shù)的分布式算法設(shè)計(jì)

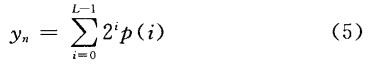

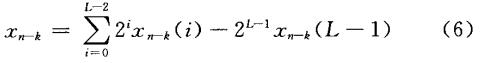

對(duì)于有符號(hào)數(shù)的補(bǔ)碼表示為:

則由式(5),式(1)可得:

2. 分布式的濾波器的軟件實(shí)現(xiàn)

從式(5)和式(7)可以看出,利用分布式算法實(shí)現(xiàn)一個(gè)N項(xiàng)乘積和,關(guān)鍵是如何實(shí)現(xiàn)式(4)中乘積項(xiàng)及各乘積項(xiàng)之和。

在FPGA中可以預(yù)先設(shè)定一個(gè)N位輸入的查找表來實(shí)現(xiàn)部分乘積項(xiàng),即預(yù)先設(shè)定N階濾波系統(tǒng)查找表,實(shí)現(xiàn)向量x(i)={x0(i),x1(i),x2(i),…,xN-1(i))到p(i)的一個(gè)映射。由于查找表的地址空間與階數(shù)成指數(shù)關(guān)系(2N),完全用查找表來實(shí)現(xiàn)部分乘積項(xiàng)需要容量很大的存儲(chǔ)器,這就需要占用巨大的資源,而且功耗增加、速度降低。因此為了減小設(shè)計(jì)規(guī)模,可以將一個(gè)大的查找表分為幾個(gè)較小的查找表來實(shí)現(xiàn)。例如,本系統(tǒng)采用的8階FIR濾波器,則用一個(gè)查找表來實(shí)現(xiàn)需要256(28)位地址空間的ROM,將8階FIR濾波器分成兩個(gè)4階FIR濾波器實(shí)現(xiàn),只需要2個(gè)16(24)位地址空間的ROM,這樣大大地降低了設(shè)計(jì)規(guī)模和資源使用量。把輸入x(i)作為地址,分為高四位和低四位地址進(jìn)行查找。表1給出了8階濾波系統(tǒng)的低四位地址x(i)與p(i)的映射關(guān)系。

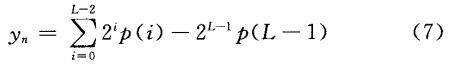

本系統(tǒng)中濾波器系統(tǒng)函數(shù)采用Matlab中的fdatool工具,并根據(jù)設(shè)計(jì)要求采用了kaiser窗設(shè)計(jì)出濾波器的系統(tǒng)函數(shù)h(n),其采樣頻率為500 kHz,通頻帶帶寬為100 Hz。設(shè)計(jì)的低通濾波器如圖1所示。若需實(shí)現(xiàn)高通或帶通濾波器,只需在設(shè)計(jì)時(shí)利用高通或帶通濾波器代替低通濾波器即可。

圖1 低通濾波器

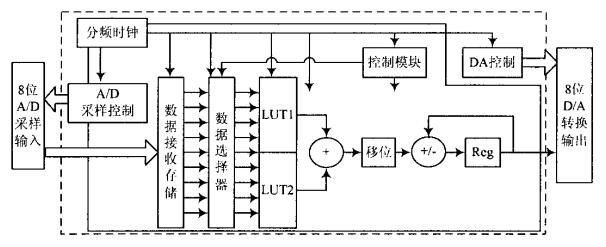

利用Verilog硬件描述語言設(shè)計(jì)本系統(tǒng)軟件,系統(tǒng)主要分為以下4個(gè)部分。包括頂層文件、A/D采樣、算法實(shí)現(xiàn)和D/A轉(zhuǎn)換。系統(tǒng)總體結(jié)構(gòu)如圖2所示。

圖2 系統(tǒng)整體框圖

由于FPGA頻率為100 MHz,采用的DAC0809轉(zhuǎn)換頻率必須小于1 MHz,所以在頂層文件對(duì)系統(tǒng)時(shí)鐘進(jìn)行200分頻,提供外圍所需時(shí)鐘。然后對(duì)各模塊進(jìn)行例化,使之成為完整的系統(tǒng)。

對(duì)A/D采樣輸入3位地址,并使ALE=1,將地址存入地址鎖存器中。此地址經(jīng)譯碼選通8路模擬輸入之一到比較器。START上升沿將逐次逼近寄存器復(fù)位。下降沿時(shí)啟動(dòng)A/D轉(zhuǎn)換,之后EOC輸出信號(hào)變低,指示轉(zhuǎn)換正在進(jìn)行。直到完成A/D轉(zhuǎn)換,EOC變?yōu)楦唠娖?,指示A/D轉(zhuǎn)換結(jié)束,結(jié)果數(shù)據(jù)已存入鎖存器,這個(gè)信號(hào)可用作中斷申請。當(dāng)OE輸入高電平時(shí),輸出三態(tài)門打開,轉(zhuǎn)換結(jié)果的數(shù)字量輸出到數(shù)據(jù)總線上。CLK為時(shí)鐘輸入信號(hào)線。由頂層文件的分頻時(shí)鐘提供500 kHz時(shí)鐘,對(duì)信號(hào)進(jìn)行采集。

算法主體的實(shí)現(xiàn)主要由以下幾個(gè)部分組成:數(shù)據(jù)接收存儲(chǔ)、數(shù)據(jù)選擇器、2個(gè)存儲(chǔ)器、加法和控制部分。

數(shù)據(jù)接收是在每個(gè)時(shí)鐘下降沿時(shí)檢測轉(zhuǎn)換完成信號(hào),如果完成,則存入對(duì)應(yīng)的存儲(chǔ)器中,對(duì)于N階的系統(tǒng),就需要存儲(chǔ)N個(gè)數(shù)據(jù)等待處理。然后利用數(shù)據(jù)選擇器依次選擇各個(gè)數(shù)據(jù),對(duì)數(shù)據(jù)的每一位進(jìn)行檢測和提取,組成算法中所需要的數(shù)據(jù)。在控制信號(hào)的作用下利用累加器對(duì)數(shù)據(jù)疊加、移位處理即可實(shí)現(xiàn)。

最后,F(xiàn)PGA向DAC0832的數(shù)據(jù)輸入口(D10~D17)輸送數(shù)據(jù)。提供DAC0832數(shù)據(jù)鎖存允許控制信號(hào)ILE,高電平有效。提供DAC0832控制信號(hào)(CS:片選信號(hào);Xfer:數(shù)據(jù)傳輸控制信號(hào);WRl、WR2:DAC寄存器寫選通信號(hào)),低電平有效。

3.仿真實(shí)驗(yàn)、工況信號(hào)測試實(shí)驗(yàn)

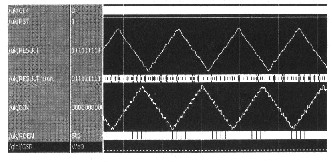

基于分布式算法低通FIR濾波器選用Xilinx公司的Virtex-Ⅱpro器件,在ISEl0.1下進(jìn)行設(shè)計(jì)。利用modelsim 6.5對(duì)濾波器進(jìn)行仿真。系統(tǒng)采用頻率為500 kHz的分頻時(shí)鐘,在FPGA中產(chǎn)生一個(gè)高頻方波和一個(gè)低頻鋸齒波信號(hào),并對(duì)兩個(gè)信號(hào)進(jìn)行疊加。疊加后的信號(hào)作為輸入,對(duì)應(yīng)圖中DIN,經(jīng)過系統(tǒng)處理后輸出結(jié)果對(duì)應(yīng)圖中RESULT,仿真結(jié)果如圖3所示。

圖3 軟件仿真

由圖3中可以看出,本系統(tǒng)存在相位偏移和濾波后依然存在雜波信號(hào)的缺點(diǎn),相位偏移主要是由濾波處理滯后于輸入引起的,比較穩(wěn)定且偏移較小,一般情況下可以忽略;雜波信號(hào)由系統(tǒng)階數(shù)較低和系數(shù)量化誤差引起的。實(shí)際應(yīng)用中可根據(jù)情況選擇適當(dāng)階數(shù)的濾波器和提高采樣頻率予以解決。

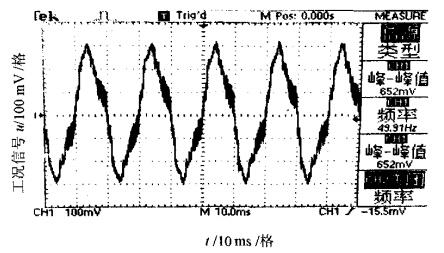

工況信號(hào)測試實(shí)驗(yàn)。由信號(hào)發(fā)生器同時(shí)產(chǎn)生一個(gè)50 Hz低頻信號(hào)和一個(gè)5 kHz高頻信號(hào),然后對(duì)兩個(gè)信號(hào)進(jìn)行疊加,作為被測的工況信號(hào)。被測的工況信號(hào)經(jīng)過A/D轉(zhuǎn)換、濾波處理、D/A轉(zhuǎn)換,然后在示波器中顯示,如圖4所示。輸出波形中過濾掉了高頻信號(hào)部分,同時(shí)低頻信號(hào)能夠通過該濾波器。由圖4中可以看出,濾波處理后與實(shí)際信號(hào)還存在一定的誤差。誤差主要是由于算法中采用了低階濾波器、系數(shù)量化誤差、器件精度低等原因所致,該誤差可以控制在允許范圍,還可以通過選擇高精度的器件和增加濾波器的階數(shù)得以提高。

圖4 實(shí)際測試

結(jié)語

本文總結(jié)了基于分布式算法的低通FIR濾波器設(shè)計(jì)方案,經(jīng)實(shí)驗(yàn)結(jié)果表明,該濾波器工作可靠,濾波精度較高,且具有占用資源少,運(yùn)算速度快。在資源允許的條件下可根據(jù)實(shí)際應(yīng)用任意確定濾波器的字長和階數(shù),在高速數(shù)字信號(hào)處理領(lǐng)域可以得到很好的應(yīng)用。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號(hào)碼或加QQ/微信,由我們的銷售經(jīng)理給您精準(zhǔn)的報(bào)價(jià)以及產(chǎn)品介紹