本文介紹了使用AD9854芯片和FPGA,并基于DDS理論設(shè)計并實現(xiàn)了多模式多波形雷達信號源。它可模擬LFM、NLFM、單頻、相位鳊碼等多種脈沖信號波形,能有效驗證脈沖壓縮與信號處理單元的工作性能。測試結(jié)果表明,該系統(tǒng)能滿足設(shè)計要求。

1.雷達信號源設(shè)計要求

雷達信號源的設(shè)計在雷達測試中有著非常重要的作用。本文設(shè)計的雷達信號源要求實現(xiàn)三個功能:

(1)要求該系統(tǒng)能產(chǎn)生多種波形信號,包括:線性調(diào)頻信號,非線性調(diào)頻信號等。要求信號的指標都能夠達到要求。

(2)要求能模擬雷達回波,能夠?qū)π盘栠M行延時,使信號能夠在距離波門內(nèi),來滿足信號處理機的要求;并且能夠在信號中加入多普勒頻移,使信號處理機可以測試測速模塊的性能。要求該信號源能有效地驗證脈沖壓縮與信號處理單元的工作性能,評估系統(tǒng)的分辨力。

(3)與外部通信。該信號源與整個雷達系統(tǒng)是相參的,使用同一個時鐘,保證該模塊與整個系統(tǒng)是同步工作的。該模塊受外部控制,主要是從RS 422接口接收由定時板發(fā)送過來的差分信號;當接收到觸發(fā)信號時,就開始產(chǎn)生信號;當接收脈沖選擇信號的時候,進行模式轉(zhuǎn)換,能產(chǎn)生8種模式的信號。

DDS在相對帶寬、頻率轉(zhuǎn)換時間、相位連續(xù)性、正交輸出、高分辨力以及集成化等方面都遠遠超過了傳統(tǒng)頻率合成技術(shù)所能達到的水平,為系統(tǒng)提供了優(yōu)于模擬信號源的性能。

FPGA具有集成度高、通用性好、設(shè)計靈活、編程方便等諸多優(yōu)點,因此采用AD9854和FPGA來設(shè)計雷達信號源。

2.系統(tǒng)方案概述

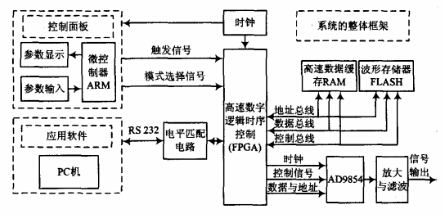

根據(jù)雷達信號源系統(tǒng)設(shè)計的要求,總體框圖如圖1所示。該系統(tǒng)主要由FPGA時序控制部分、AD9854頻率合成部分、波形存儲三部分組成。在此重點闡述FPGA設(shè)計和AD9854硬件設(shè)計兩部分。

圖1 系統(tǒng)原理框圖

系統(tǒng)的主體部分主要由高速數(shù)字邏輯時序控制模塊(FPGA)和DDS芯片AD9854構(gòu)成,還包括放大模塊、濾波模塊、存儲模塊、時鐘模塊、電源模塊。該部分通過FPGA對整個電路的數(shù)字部分進行時序控制,包括給AD9854發(fā)送數(shù)據(jù)、地址、時鐘以及控制信號。AD9854是DDS芯片,能產(chǎn)生所需要的信號。存儲部分采用了FLASH和SRAM;FLASH主要用來存儲波形文件,而SRAM主要是在開機時暫存數(shù)據(jù)文件。

通過控制面板發(fā)送觸發(fā)信號和模式選擇信號對系統(tǒng)信號產(chǎn)生進行控制。當FPGA接收到觸發(fā)信號時,F(xiàn)PGA才開始工作,并且給AD9854發(fā)送數(shù)據(jù)以產(chǎn)生信號。模式選擇信號是3位的二進制數(shù),可以產(chǎn)生8種狀態(tài)??刂泼姘搴虵PGA通過RS 422電平相連,通過差分數(shù)據(jù)線來傳輸數(shù)據(jù)。

PC機應(yīng)用軟件完成所需各種軟件的波形數(shù)據(jù)的計算,包括起始頻率FTW,頻率分辨率DFW,時間分辨率RRC等數(shù)據(jù),然后將所得的數(shù)據(jù)轉(zhuǎn)化成.dat格式。PC通過串口與系統(tǒng)主板進行數(shù)據(jù)通信,通過MAX3232進行電平轉(zhuǎn)化。數(shù)據(jù)最后存儲到主板的存儲器中(FLASH和SRAM);當系統(tǒng)工作時,F(xiàn)PGA從FLASH中讀取波形文件來產(chǎn)生信號。

3.AD9854模塊

3.1AD9854芯片介紹

數(shù)字頻率合成芯片AD9854是用于高端DDS技術(shù)的一款芯片,如圖2所示。該芯片帶有兩個高速、高性能的正交D/A轉(zhuǎn)換器,可以同時輸出I/Q兩路正交信號。當參考時鐘源很精確時,AD9854能夠產(chǎn)生高穩(wěn)定度的,頻率、相位、幅度均可編程的正弦和余弦曲線,被廣泛地應(yīng)用于通信、雷達、儀器等應(yīng)用領(lǐng)域。AD9854的高速DDS內(nèi)核能夠提供48 B的相位累加器和頻率累加器(在300 MHz的系統(tǒng)時鐘下,可達1μHz的頻率分辨率);其中17 B的相位-幅度映射位數(shù)能夠確保該芯片優(yōu)良的無雜散動態(tài)范圍(SFDR)性能。

圖2 AD9854芯片

3.2AD9854芯片特點

(1)300 MHz內(nèi)部時鐘速率

(2)FSK、BPSK、PSK、線性調(diào)頻、AM操作

(3)兩個集成式12位數(shù)模轉(zhuǎn)換器(DAC)

(4)超高速比較器,均方根抖動:3 ps

(5)出色的動態(tài)性能:80 dB SFDR (100 MHz ± 1 MHz AOUT)

(6)4×至20×可編程基準時鐘乘法器

(7)兩個48位可編程頻率寄存器

(8)兩個14位可編程相位偏移寄存器

(9)12位可編程振幅調(diào)制和開關(guān)輸出形鍵控功能

(10)單引腳FSK和BPSK數(shù)據(jù)接口

(11)通過輸入/輸出接口提供PSK功能

(12)線性或非線性FM線性調(diào)頻功能,具有單引腳頻率保持功能

3.3AD9854芯片工作模式

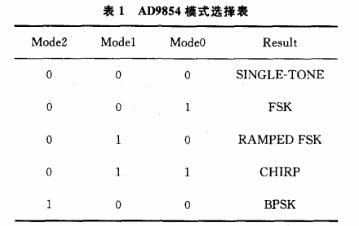

AD9854具有5種可編程操作模式,通過改變控制寄存器(并行尋址方式下的地址為1FH)的控制位即可以選擇相應(yīng)的模式。根據(jù)本方案,主要對單頻(Single Tone)模式和調(diào)頻(Chirp)模式進行探討。5種模式的選擇表如表1所示。

(1)單頻模式

系統(tǒng)上電或硬件復(fù)位時,AD9854自動進入該默認模式,此時芯片輸出的信號是直流信號。當對頻率控制字進行設(shè)定后,即可輸出單頻信號。

(2)調(diào)頻模式

此處的調(diào)頻模式即為常見的脈沖調(diào)頻模式。AD9854同時支持線性和非線性這兩種調(diào)頻模式。該雷達信號源要求既能產(chǎn)生線性調(diào)頻信號,也能產(chǎn)生非線性調(diào)頻信號,所以AD9854完全能滿足要求。脈沖調(diào)頻信號的時寬主要是由update clock來決定。當?shù)谝粋€update clock信號到來時,AD9854把I/O緩存中的FTW,DFW,RRC以及其他的控制字都送到可編程寄存器中,AD9854開始工作。當脈沖調(diào)頻信號結(jié)束時,通過FPGA再發(fā)送一個update clock信號,然后就把I/O緩存中的清零數(shù)據(jù)送入了可編程寄存器中。

4.系統(tǒng)硬件實現(xiàn)

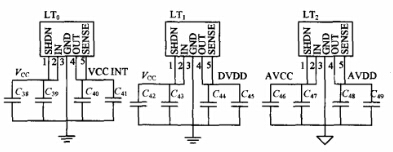

4.1電源和時鐘設(shè)計

在該系統(tǒng)中,采用線性電源LT1764進行電平轉(zhuǎn)換,把5 V轉(zhuǎn)成3.3 V和1.5 V,為FPGA和AD9854等芯片提供電源。濾波電容分為旁路電容和去耦電容。旁路電容把前級攜帶的高頻雜波濾去,還可以有效地旁路地和電源上的地彈噪聲。旁路電容一般容值都比較小,根據(jù)諧振頻率一般是0.1μF和0.01μF。去耦電容也稱退耦電容,是把輸出信號的干擾作為濾除的對象。去耦電容一般比較大,取值為47μF和10μF。如圖3所示。

圖3 電源模塊

時鐘電路與FPGA的電源面要隔離開(可以在同一個層),只通過鐵氧體磁珠(ferritebead)相連。鐵氧體磁珠在低頻時阻抗很低,而在高頻時阻抗很高,可以抑制高頻干擾,這樣外面的高頻干擾不會影響時鐘芯片,而時鐘芯片內(nèi)部產(chǎn)生的振蕩信號也不會影響到外面的電路。時鐘部分的地和整個PCB的地是一個統(tǒng)一的整體,不要分割。

在時鐘芯片的電源引腳處放一個容值為10μF的鉭電容,不僅可以防止由于電壓波動引起的電流涌動,還可以抑制低頻干擾;同時大電容的后面并聯(lián)一個0.1μF的小電容,且所放的位置要盡可能地靠近電源引腳,這樣可以減小外來的電源噪聲。在靠近時鐘輸出的引腳要串接一個50 Ω的電阻以減小輸出電流,提高時鐘波形的質(zhì)量。時鐘線盡量少使用過孔,因為過孔使阻抗發(fā)生變化,影響信號的質(zhì)量,進而產(chǎn)生EMI輻射和抖動問題。

4.2存儲模塊設(shè)計

在該系統(tǒng)中,采用FLASH和SRAM作為存儲器。FLASH主要用于存儲波形文件,掉電時,數(shù)據(jù)也不會丟失。而SRAM是做高速數(shù)據(jù)緩存的,掉電后數(shù)據(jù)會丟失。首先FPGA從FLASH中讀取波形文件,然后再存儲到SRAM中,需要這些波形數(shù)據(jù)時候,再從SRAM中去讀取。這樣的設(shè)計是因為FLASH的讀/寫速度比較慢,而SRAM的讀/寫速度比較快。但是FLASH中的數(shù)據(jù)掉電不會丟失,而SRAM中的數(shù)據(jù)掉電要丟失。

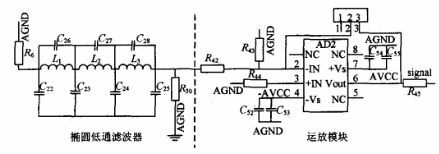

4.3放大及濾波電路設(shè)計

為了提高DDS信號產(chǎn)生系統(tǒng)的帶負載能力,同時實現(xiàn)AD9854芯片內(nèi)嵌數(shù)/模轉(zhuǎn)換器輸出的電流轉(zhuǎn)換,需要在其后加入運算放大器(見圖4)。該運算放大器性能的好壞將決定信號的輸出質(zhì)量及系統(tǒng)帶負載的能力。由于方案中信號輸出的最高頻率為120 MHz,所以應(yīng)保證放大器在較高頻率范圍內(nèi)具有很好的線性度,防止放大器自激。根據(jù)頻率源的設(shè)計要求,該方案中的放大器模塊應(yīng)滿足以下要求:放大器的增益可調(diào)、放大器的帶寬應(yīng)大于120 MHz、輸出帶載能力強、信號輸出質(zhì)量較好。綜合以上要求,選擇ADI公司的寬帶運算放大器AD8014作為放大器模塊的核心器件。AD8014的主要性能特點有:低功耗;穩(wěn)定增益G=1;高速,Slew Rate 4 000 V/μs,24 ns的建立時間;

在該方案中,放大電路采用串連電壓負反饋-反相比例放大電路。

圖4 橢圓低通濾波器及放大模塊電路圖

采用串聯(lián)電壓負反饋將使放大器的輸入阻抗增大,輸出阻抗減小,提高電路輸出信號的帶負載的能力。在電路中,反饋電阻R16采用可調(diào)電阻,使電路的增益可調(diào);同時在放大器的正、負電源輸入端加電容去藕濾波電路,以減小電源紋波對放大器的影響。

根據(jù)AD8014的要求,在進行PCB布線時,需在其周圍均鋪上了地網(wǎng);但是,為了降低寄生電容對電路輸入的影響,其輸入腳附近沒有鋪地。在進行器件布局時,反饋電阻R16應(yīng)盡量靠近AD8014的反向輸入端。

為使中頻模擬器有較好的通用性,而雷達中頻變化范圍較寬,考慮到在濾除諧波分量的同時要盡可能減少相位的不連續(xù)性,因此設(shè)計了一個帶寬為40MHz的9階無源低通濾波器。

5.FPGA實現(xiàn)

5.1FPGA設(shè)計概述

FPGA用于建立與DDS芯片(AD9854),F(xiàn)LASH(E28F128J3A)以及SRAM(IS61LV10248)之間的聯(lián)系,主要負責以下兩個方面:

(1)發(fā)送DDS控制字并控制DDS芯片的時序;

(2)控制存儲芯片的時序,并發(fā)送或讀取所要存儲的波形數(shù)據(jù)。FPGA內(nèi)部采用原理圖和Verilog HDL相結(jié)合的方式進行軟件設(shè)計。

下面重點介紹DDS控制部分的實現(xiàn)。

5.2DDS控制模塊

DDS控制模塊負責讀取片內(nèi)雙口RAM中的DDS控制字,并將AD9854的時序?qū)懭隓DS芯片,控制DDS的工作。

DDS控制模塊在每次寫AD9854控制字之前先對RAM發(fā)出讀使能,同時給出讀地址,讀取當前控制字,然后按照時序要求寫入DDS芯片。Quartus中仿真的時序圖如圖5所示。

圖5 FPGA給AD9854送數(shù)的時序仿真圖

以下將介紹控制AD9854的流程。

首先對AD9854進行復(fù)位,F(xiàn)PGA發(fā)送高電平給AD9854第71管腳,高電平持續(xù)的時間長度要超過20個周期的AD9854采樣時鐘。復(fù)位信號使AD9854的所有寄存器恢復(fù)到默認狀態(tài)。需要注意的是,復(fù)位信號的長度必須滿足一定的要求,否則在實際操作中可能會出現(xiàn)錯誤。

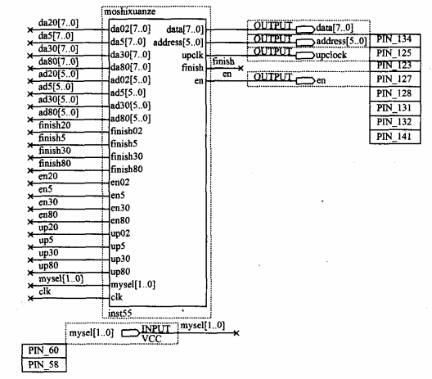

當FPGA接收到外部發(fā)送的觸發(fā)信號以后,DDS控制模塊就開始工作了。首先從雙口RAM中讀取波形數(shù)據(jù),包括起始頻率(FTW),增量頻率字(DFW),斜率時鐘(RRC)以及控制信號。DDS控制模塊給雙口RAM送讀使能和讀地址,然后把雙口RAM中的數(shù)據(jù)讀到數(shù)據(jù)選擇模塊中。之后接收波形模式選擇信號。這個信號是三位二進制數(shù),總共有8種工作模式,總的來說分為工作模式和測試模式。當系統(tǒng)為工作模式的時候,該系統(tǒng)就是雷達發(fā)射機的中頻信號模塊。在工作模式下,該中頻信號模塊能發(fā)射4種模式的波形:時寬是0.2μs的正弦波,時寬為5μs的線性調(diào)頻波,時寬為30μs的線性調(diào)頻波和時寬80μs的線性調(diào)頻波。當發(fā)射信號為時寬是0.2μs的正弦波或時寬為5μs的線性調(diào)頻波時,對近區(qū)的目標進行搜索;當發(fā)射信號是時寬為30μs的線性調(diào)頻波時,對中區(qū)的目標進行搜索;當發(fā)射信號為時寬為80μs的線性調(diào)頻波時,對遠區(qū)的目標進行搜索。當系統(tǒng)為測試模式的時候,也分為時寬為0.2μs,5μs,30μs,80μs這4種模式的信號,但是當信號時寬為0.2μs時,信號中加入了多普勒頻率,這樣就為信號處理機檢測測速單元提供了方便。該系統(tǒng)為測試模式時主要且模擬雷達回波信號的作用。如圖6所示。

圖6 模式選擇模塊

當接收到模式選擇信號以后,DDS控制模塊開始給AD9854送數(shù)據(jù)。這時,F(xiàn)PGA給AD9854傳送的數(shù)據(jù)都保存在I/O緩存區(qū)內(nèi)。接著,F(xiàn)PGA就給AD9854發(fā)送update clock。這樣,I/O緩存區(qū)內(nèi)的數(shù)據(jù)就送入AD9854的寄存器中,AD9854開始產(chǎn)生信號。最后,給AD9854的控制寄存器地址為1F的第七位送高電平,這樣就把信號清零,從而產(chǎn)生了脈沖信號。

6.系統(tǒng)測試

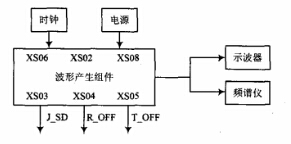

6.1系統(tǒng)測試框圖

根據(jù)該設(shè)計系統(tǒng)的設(shè)計思想和工作原理,結(jié)合系統(tǒng)測試指標要求,提出系統(tǒng)測試方案和使用儀器。測試儀表主要包括信號源、頻譜儀、萬用表、電源、示波器等。

按照框圖連接測試儀表,設(shè)置直流電源輸出電壓為±5 V,通過相應(yīng)接口送入雷達信號產(chǎn)生器的電源接口。設(shè)置信號源,輸出中心頻率為30 MHz,功率為(0±1)dBm線性調(diào)頻波。測試時雷達信號產(chǎn)生器工作于外觸發(fā)模式下,當接收到外部觸發(fā)信號時開始產(chǎn)生波形。雷達信號源的信號送入示波器(泰克的DPO4104),測試信號的時域參數(shù),包括時寬,幅度,脈沖前后沿,本底噪聲等。雷達信號源的信號送入頻譜儀(羅德與施瓦茨的頻譜儀FSMR)測試信號的頻域參數(shù),包括信號的頻率、帶寬、諧波和帶內(nèi)雜散等。

系統(tǒng)測試框圖如圖7所示。

圖7 波形產(chǎn)生測試框圖

6.2系統(tǒng)測試結(jié)果

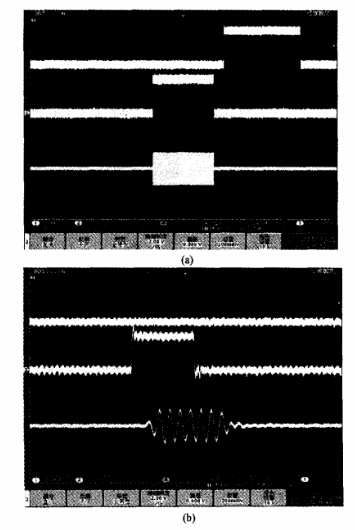

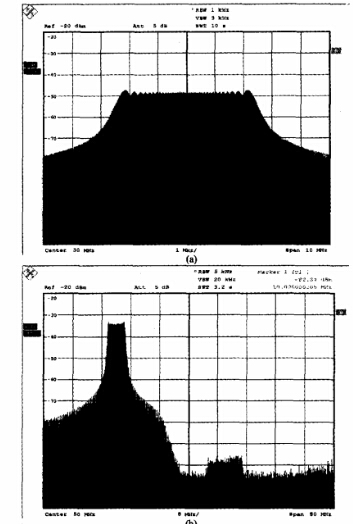

時域測試結(jié)果如圖8所示。

圖8 時寬為80μs以及0.2μs的信號

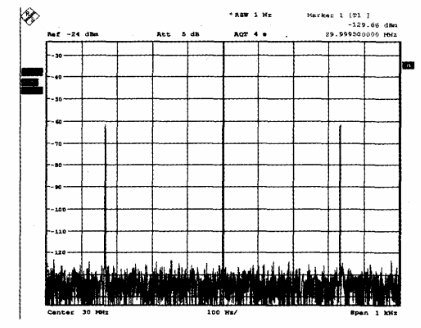

圖9圖10為頻域測試結(jié)果。

圖9 信號頻譜及測試諧波抑制圖

圖10 測試帶內(nèi)雜數(shù)

通過測試結(jié)果分析,可見該雷達信號產(chǎn)生器系統(tǒng)可產(chǎn)生多種不同時寬、帶寬和脈沖重復(fù)頻率的LFM、NLFM、脈沖信號,能夠滿足工程應(yīng)用的需要。

結(jié)語

通過對雷達信號源的工程實現(xiàn)進行研究,利用DDS芯片和FPGA實現(xiàn)了多模式多波形的雷達信號源。通過優(yōu)化硬件設(shè)計,改進系統(tǒng)的結(jié)構(gòu),優(yōu)化了系統(tǒng)的性能,并給出系統(tǒng)實際測試的結(jié)果。為DDS實現(xiàn)雷達信號源提供了設(shè)計參考。

電話:18923864027(同微信)

QQ:709211280

〈烜芯微/XXW〉專業(yè)制造二極管,三極管,MOS管,橋堆等,20年,工廠直銷省20%,上萬家電路電器生產(chǎn)企業(yè)選用,專業(yè)的工程師幫您穩(wěn)定好每一批產(chǎn)品,如果您有遇到什么需要幫助解決的,可以直接聯(lián)系下方的聯(lián)系號碼或加QQ/微信,由我們的銷售經(jīng)理給您精準的報價以及產(chǎn)品介紹